| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| 71V2558SA166BG | IDT |

获取价格 |

ZBT SRAM, 256KX18, 3.5ns, CMOS, PBGA119, 14 X 22 MM, PLASTIC, MS-028AA, BGA-119 |

|

| 71V2558SA166BGGI8 | IDT |

获取价格 |

ZBT SRAM, 256KX18, 3.5ns, CMOS, PBGA119 |

|

| 71V2558SA166BQGI8 | IDT |

获取价格 |

ZBT SRAM, 256KX18, 3.5ns, CMOS, PBGA165 |

|

| 71V2558SA166BQI | IDT |

获取价格 |

ZBT SRAM, 256KX18, 3.5ns, CMOS, PBGA165, 13 X 15 MM, FPBGA-165 |

|

| 71V2558SA200BG8 | IDT |

获取价格 |

ZBT SRAM, 256KX18, 3.2ns, CMOS, PBGA119 |

|

| 71V2558SA200BGG | IDT |

获取价格 |

ZBT SRAM, 256KX18, 3.2ns, CMOS, PBGA119, 22 X 14 MM, ROHS COMPLIANT, PLASTIC, MS-028AA, BG |

|

| 71V2558SA200BQ | IDT |

获取价格 |

ZBT SRAM, 256KX18, 3.2ns, CMOS, PBGA165, 13 X 15 MM, FPBGA-165 |

|

| 71V2558SA200BQG | IDT |

获取价格 |

ZBT SRAM, 256KX18, 3.2ns, CMOS, PBGA165, 15 X 13 MM, ROHS COMPLIANT, FBGA-165 |

|

| 71V2558XS100BGG | IDT |

获取价格 |

ZBT SRAM, 256KX18, 5ns, CMOS, PBGA119, 22 X 14 MM, ROHS COMPLIANT, PLASTIC, MS-028AA, BGA- |

|

| 71V2558XS100BGG8 | IDT |

获取价格 |

ZBT SRAM, 256KX18, 5ns, CMOS, PBGA119 |

|

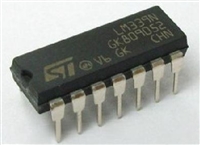

LM339N参数手册 :四路电压比较器的深度解读

LM339N参数手册 :四路电压比较器的深度解读

MMBT2222A资料手册:特性、应用、电气参数及替换型号推荐

MMBT2222A资料手册:特性、应用、电气参数及替换型号推荐

解读TDA7265手册资料:引脚说明 、电气参数及替换型号推荐

解读TDA7265手册资料:引脚说明 、电气参数及替换型号推荐

深入解读ULN2803A资料手册:引脚功能、电气参数、特性

深入解读ULN2803A资料手册:引脚功能、电气参数、特性