| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| 7008L20GGI | IDT | Multi-Port SRAM, 64KX8, 20ns, CMOS, CPGA84 |

获取价格 |

|

| 7008L20GGI8 | IDT | HIGH-SPEED 64K x 8 DUAL-PORT STATIC RAM |

获取价格 |

|

| 7008L20GI | IDT | Dual-Port SRAM, 64KX8, 20ns, CMOS, CPGA84, 1.120 X 1.120 INCH, 0.160 INCH HEIGHT, CERAMIC, |

获取价格 |

|

| 7008L20JG | IDT | Multi-Port SRAM, 64KX8, 20ns, CMOS, PQCC84 |

获取价格 |

|

| 7008L20JG8 | IDT | HIGH-SPEED 64K x 8 DUAL-PORT STATIC RAM |

获取价格 |

|

| 7008L20JGI | IDT | HIGH-SPEED 64K x 8 DUAL-PORT STATIC RAM |

获取价格 |

|

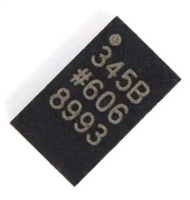

ADXL345传感器工作原理、参数分析、引脚说明

ADXL345传感器工作原理、参数分析、引脚说明

一文带你了解,DAC0832工作原理、输出电压范围、分辨率等参数

一文带你了解,DAC0832工作原理、输出电压范围、分辨率等参数

ACS712电流检测使用指南及资料手册参数分析

ACS712电流检测使用指南及资料手册参数分析

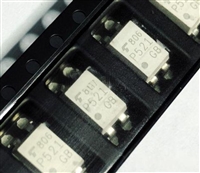

TLP521资料手册解读:参数分析、引脚说明、典型电路

TLP521资料手册解读:参数分析、引脚说明、典型电路