| 品牌 | Logo | 应用领域 |

| 意法半导体 - STMICROELECTRONICS | 外围集成电路 | |

| 页数 | 文件大小 | 规格书 |

| 181页 | 1423K |  |

| 描述 | ||

| RISC MICROCONTROLLER | ||

| 生命周期: | Obsolete | 包装说明: | , |

| Reach Compliance Code: | unknown | 风险等级: | 5.84 |

| 技术: | CMOS | uPs/uCs/外围集成电路类型: | MICROCONTROLLER, RISC |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| UPSD3214BV-24U6T | STMICROELECTRONICS | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

获取价格 |

|

| UPSD3214BV-40T1 | STMICROELECTRONICS | Flash Programmable System Device with 8032 Microcontroller Core |

获取价格 |

|

| UPSD3214BV-40T1F | STMICROELECTRONICS | 暂无描述 |

获取价格 |

|

| UPSD3214BV-40T1T | STMICROELECTRONICS | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

获取价格 |

|

| UPSD3214BV-40T6 | STMICROELECTRONICS | Flash Programmable System Device with 8032 Microcontroller Core |

获取价格 |

|

| UPSD3214BV-40T6T | STMICROELECTRONICS | Flash Programmable System Devices with 8032 Microcontroller Core and 64Kbit SRAM |

获取价格 |

|

MAX3485芯片手册参数分析及替代型号推荐

MAX3485芯片手册参数分析及替代型号推荐

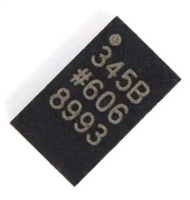

ADXL345传感器工作原理、参数分析、引脚说明

ADXL345传感器工作原理、参数分析、引脚说明

一文带你了解,DAC0832工作原理、输出电压范围、分辨率等参数

一文带你了解,DAC0832工作原理、输出电压范围、分辨率等参数

ACS712电流检测使用指南及资料手册参数分析

ACS712电流检测使用指南及资料手册参数分析