| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| SSTVF16859BG-T | IDT |

获取价格 |

Bus Driver, PDSO64 |

|

| SSTVF16859BS | NXP |

获取价格 |

13-bit 1:2 SSTL_2 registered buffer for DDR |

|

| SSTVF16859BS,118 | NXP |

获取价格 |

IC SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PQCC56, 8 X 8 MM, 0.85 M |

|

| SSTVF16859BS,151 | NXP |

获取价格 |

IC SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PQCC56, 8 X 8 MM, 0.85 M |

|

| SSTVF16859BS,157 | NXP |

获取价格 |

IC SSTV SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PQCC56, 8 X 8 MM, 0.85 M |

|

| SSTVF16859DGG | NXP |

获取价格 |

13-bit 1:2 SSTL_2 registered buffer for DDR |

|

| SSTVF16859EC | NXP |

获取价格 |

13-bit 1:2 SSTL_2 registered buffer for DDR |

|

| SSTVF16859EC,518 | NXP |

获取价格 |

SSTVF16859 - 13-bit 1 : 2 SSTL_2 registered buffer for DDR |

|

| SSTVF16859EC,551 | NXP |

获取价格 |

SSTVF16859 - 13-bit 1 : 2 SSTL_2 registered buffer for DDR |

|

| SSTVF16859EC,557 | NXP |

获取价格 |

SSTVF16859 - 13-bit 1 : 2 SSTL_2 registered buffer for DDR |

|

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

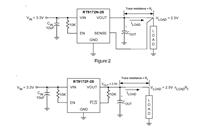

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明

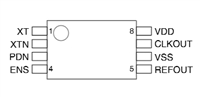

一文带你了解SM8760CA资料:主要参数特征

一文带你了解SM8760CA资料:主要参数特征