| 型号 | 品牌 | 替代类型 | 描述 | 数据表 |

| SN74LVC16374DGGR | TI |

完全替代  |

16-Bit Edge-Triggered D-Type Flip-Flop With 3-State Outputs 48-TSSOP -40 to 85 |

|

| SN74LVC16374DL | TI |

类似代替  |

16-BIT EDGE-TRIGGERED D-TYPE FLIP-FLOP WITH 3-STATE OUTPUTS |

|

| SN74LVC16374ADLR | TI |

类似代替  |

16 BIT EDGE TRIGGERED D TYPE FLIP FLOP WITH 3 STATE OUTPUTS |

|

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| SN74LVC16543 | TI |

获取价格 |

16-BIT REGISTERED TRANSCEIVER WITH 3-STATE OUTPUTS |

|

| SN74LVC16543DGG | TI |

获取价格 |

16-BIT REGISTERED TRANSCEIVER WITH 3-STATE OUTPUTS |

|

| SN74LVC16543DGGR | TI |

获取价格 |

16-Bit Registered Transceiver With 3-State Outputs 56-TSSOP |

|

| SN74LVC16543DL | TI |

获取价格 |

16-BIT REGISTERED TRANSCEIVER WITH 3-STATE OUTPUTS |

|

| SN74LVC16543DLR | TI |

获取价格 |

16-Bit Registered Transceiver With 3-State Outputs 56-SSOP -40 to 85 |

|

| SN74LVC16646 | TI |

获取价格 |

16-BIT BUS TRANSCEIVER AND REGISTER WITH 3-STATE OUTPUTS |

|

| SN74LVC16646A | TI |

获取价格 |

16-BIT BUS TRANSCEIVER AND REGISTER WITH 3-STATE OUTPUTS |

|

| SN74LVC16646ADGG | TI |

获取价格 |

LVC/LCX/Z SERIES, DUAL 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56, PLASTIC, TSSOP-5 |

|

| SN74LVC16646ADGG | ROCHESTER |

获取价格 |

LVC/LCX/Z SERIES, DUAL 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56, PLASTIC, TSSOP-5 |

|

| SN74LVC16646ADGGE4 | TI |

获取价格 |

LVC/LCX/Z SERIES, DUAL 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56, PLASTIC, TSSOP-5 |

|

芯片底部填充工艺:提升电子设备可靠性的关键步骤

芯片底部填充工艺:提升电子设备可靠性的关键步骤

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

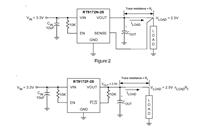

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明