| Source Url Status Check Date: | 2013-06-14 00:00:00 | 生命周期: | Obsolete |

| 零件包装代码: | TSSOP2 | 包装说明: | 4.40 MM, PLASTIC, MO-153, SOT-360-1, TSSOP-20 |

| 针数: | 20 | Reach Compliance Code: | unknown |

| 风险等级: | 5.74 | Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| PCA9561PW-T | NXP |

获取价格 |

IC QUAD 6 LINE TO 1 LINE MULTIPLEXER, TRUE OUTPUT, PDSO20, 4.40 MM, PLASTIC, MO-153, SOT-3 |

|

| PCA9564 | NXP |

获取价格 |

Parallel bus to I2C-bus controller |

|

| PCA9564_06 | NXP |

获取价格 |

Parallel bus to I2C-bus controller |

|

| PCA9564BS | NXP |

获取价格 |

Parallel bus to I2C-bus controller |

|

| PCA9564D | NXP |

获取价格 |

Parallel bus to I2C-bus controller |

|

| PCA9564D,118 | NXP |

获取价格 |

PCA9564 - Parallel bus to I2C-bus controller SOP 20-Pin |

|

| PCA9564N | NXP |

获取价格 |

Parallel bus to I2C-bus controller |

|

| PCA9564N,112 | NXP |

获取价格 |

PCA9564 - Parallel bus to I2C-bus controller DIP 20-Pin |

|

| PCA9564PW | NXP |

获取价格 |

Parallel bus to I2C-bus controller |

|

| PCA9564PW,112 | NXP |

获取价格 |

PCA9564 - Parallel bus to I2C-bus controller TSSOP2 20-Pin |

|

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

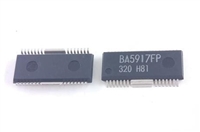

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐