| 型号 | 品牌 | 替代类型 | 描述 | 数据表 |

| NIS5101E2T1 | ONSEMI |

完全替代  |

SMART HotPlug IC/Inrush Limiter/Circuit Breaker |

|

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| NIS5102 | ONSEMI |

获取价格 |

High Side SMART HotPlug IC/Inrush Limiter/Circuit Breaker |

|

| NIS5102QP1HT1 | ONSEMI |

获取价格 |

High Side SMART HotPlug IC/Inrush Limiter/Circuit Breaker |

|

| NIS5102QP1HT1G | ONSEMI |

获取价格 |

High Side SMART HotPlug IC/Inrush Limiter/Circuit Breaker |

|

| NIS5102QP2HT1 | ONSEMI |

获取价格 |

High Side SMART HotPlug IC/Inrush Limiter/Circuit Breaker |

|

| NIS5102QP2HT1G | ONSEMI |

获取价格 |

High Side SMART HotPlug IC/Inrush Limiter/Circuit Breaker |

|

| NIS510X | ONSEMI |

获取价格 |

Low cap. diode array for 2 Line High Speed USB protection devic |

|

| NIS5112 | ONSEMI |

获取价格 |

Electronic Fuse |

|

| NIS5112_07 | ONSEMI |

获取价格 |

Electronic Fuse |

|

| NIS5112D1R2G | ONSEMI |

获取价格 |

Electronic Fuse |

|

| NIS5112D2R2G | ONSEMI |

获取价格 |

Electronic Fuse |

|

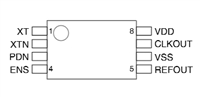

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

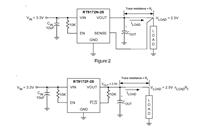

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明

一文带你了解SM8760CA资料:主要参数特征

一文带你了解SM8760CA资料:主要参数特征

解读MAX3238ECPW:一款多通道RS-232线驱动/接收器

解读MAX3238ECPW:一款多通道RS-232线驱动/接收器