MAX5700/MAX5701/

MAX5702

Ultra-Small, Dual-Channel, 8-/10-/12-Bit Buffered

Output DACs with Internal Reference

and SPI Interface

General Description

Benefits and Features

The MAX5700/MAX5701/MAX5702 2-channel, low-power,

8-/10-/12-bit, voltage-output digital-to-analog converters

(DACs) include output buffers and an internal reference

that is selectable to be 2.048V, 2.500V, or 4.096V. The

MAX5700/MAX5701/MAX5702 accept a wide supply

voltage range of 2.7V to 5.5V with extremely low power

(1.5mW) consumption to accommodate most low-voltage

applications. A precision external reference input allows

rail-to-rail operation and presents a 100kI (typ) load to

an external reference.

● Two High-Accuracy DAC Channels

• 12-Bit Accuracy Without Adjustment

• ±1 LSB INL Buffered Voltage Output

• Monotonic Over All Operating Conditions

•

Independent Mode Settings for Each DAC

● Three Precision Selectable Internal References

• 2.048V, 2.500V, or 4.096V

● Internal Output Buffer

• Rail-to-Rail Operation with External Reference

•ꢀ 4.5μsꢀSettlingꢀTime

The MAX5700/MAX5701/MAX5702 have an a 50MHz

3-wire SPI/QSPI™/MICROWIRE®/DSP-compatible serial

interface. The DAC output is buffered and has a low sup-

ply current of less than 250FA per channel and a low

offset error of Q0.5mV (typ). On power-up, the MAX5700/

MAX5701/MAX5702 reset the DAC outputs to zero, pro-

viding additional safety for applications that drive valves

or other transducers which need to be off on power-up.

The internal reference is initially powered down to allow

use of an external reference. The MAX5700/MAX5701/

MAX5702 allow simultaneous output updates using soft-

ware LOAD commands.

•ꢀ OutputsꢀDirectlyꢀDriveꢀ2kΩꢀLoads

●

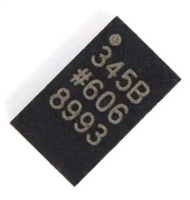

Smallꢀ5mmꢀxꢀ3mmꢀ10-PinꢀμMAXꢀorꢀUltra-Smallꢀ

3mm x 3mm 10-Pin TDFN Package

● Wide 2.7V to 5.5V Supply Range

● Separate 1.8V to 5.5V V Power-Supply Input

DDIO

● 50MHz 3-Wire SPI/QSPI/MICROWIRE/DSP

Compatible Serial Interface

● Power-On-Reset to Zero-Scale DAC Output

● CLR For Asynchronous Control

● Three Software-Selectable Power-Down Output

Impedances

A clear logic input (CLR) allows the contents of the CODE

and the DAC registers to be cleared asynchronously and

sets the DAC outputs to zero. The MAX5700/MAX5701/

MAX5702 are available in a 10-pin µMAXM and an ultra-

small, 10-pin TDFN package and are specified over the

-40NC to +125NC temperature range.

• 1kΩ,ꢀ100kΩ,ꢀorꢀHighꢀImpedance

●

Lowꢀ350μAꢀSupplyꢀCurrentꢀatꢀ3VꢀV

DD

Functional Diagram

Applications

V

DDIO

V

REF

Programmable Voltage and Current Sources

DD

MAX5700

MAX5701

MAX5702

Gain and Offset Adjustment

INTERNAL REFERENCE/

EXTERNAL BUFFER

Automatic Tuning and Optical Control

Power Amplifier Control and Biasing

Process Control and Servo Loops

Portable Instrumentation

CSB

1 OF 2 DAC CHANNELS

BUFFER

SCLK

CODE

REGISTER

DAC

LATCH

8-/10-/12-BIT

DAC

DIN

OUTA

OUTB

SPI SERIAL

INTERFACE

CLR

CLEAR/

CODE RESET

CLEAR/

LOAD RESET

Data Acquisition

100kI

1kI

POWER-DOWN

DAC CONTROL LOGIC

Ordering Information appears at end of data sheet.

POR

QSPI is a trademark of Motorola, Inc.

MICROWIRE is a registered trademark of National

Semiconductor Corporation.

GND

µMAX is a registered trademark of Maxim Integrated Products, Inc.

19-6455; Rev 2; 8/13

SS8550数据手册:应用场景、主要参数分析、特性分析

SS8550数据手册:应用场景、主要参数分析、特性分析

UC3845全面解析:资料手册参数、引脚详解、维修技巧与替代型号推荐

UC3845全面解析:资料手册参数、引脚详解、维修技巧与替代型号推荐

MAX3485芯片手册参数分析及替代型号推荐

MAX3485芯片手册参数分析及替代型号推荐

ADXL345传感器工作原理、参数分析、引脚说明

ADXL345传感器工作原理、参数分析、引脚说明