| 是否无铅: | 含铅 | 是否Rohs认证: | 不符合 |

| 生命周期: | Obsolete | Reach Compliance Code: | not_compliant |

| 风险等级: | 5.92 | 最长访问时间: | 5 ns |

| I/O 类型: | SEPARATE | JESD-30 代码: | R-XDIP-T28 |

| JESD-609代码: | e0 | 内存密度: | 16384 bit |

| 内存集成电路类型: | STANDARD SRAM | 内存宽度: | 4 |

| 负电源额定电压: | -5.2 V | 端子数量: | 28 |

| 字数: | 4096 words | 字数代码: | 4000 |

| 工作模式: | ASYNCHRONOUS | 最高工作温度: | 70 °C |

| 最低工作温度: | 组织: | 4KX4 | |

| 输出特性: | OPEN-EMITTER | 封装主体材料: | CERAMIC |

| 封装代码: | DIP | 封装等效代码: | DIP28,.4 |

| 封装形状: | RECTANGULAR | 封装形式: | IN-LINE |

| 并行/串行: | PARALLEL | 峰值回流温度(摄氏度): | 225 |

| 电源: | -5.2 V | 认证状态: | Not Qualified |

| 子类别: | SRAMs | 表面贴装: | NO |

| 温度等级: | COMMERCIAL | 端子面层: | Tin/Lead (Sn/Pb) |

| 端子形式: | THROUGH-HOLE | 端子节距: | 2.54 mm |

| 端子位置: | DUAL | 处于峰值回流温度下的最长时间: | 30 |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| IDT101A484S5E | IDT | Standard SRAM, 4KX4, 5ns, CDFP28 |

获取价格 |

|

| IDT101A484S5Y | IDT | Standard SRAM, 4KX4, 5ns, PDSO28 |

获取价格 |

|

| IDT101A484S7C | IDT | Standard SRAM, 4KX4, 7ns, CDIP28 |

获取价格 |

|

| IDT101A484S7CB | IDT | Standard SRAM, 4KX4, 7ns, CDIP28 |

获取价格 |

|

| IDT101A484S7DF | ETC | x4 SRAM |

获取价格 |

|

| IDT101A484S7E | IDT | Standard SRAM, 4KX4, 7ns, CDFP28 |

获取价格 |

|

pcf8563芯片功能说明、参数分析、引脚说明

pcf8563芯片功能说明、参数分析、引脚说明

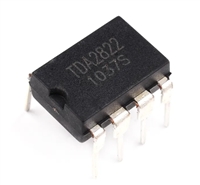

TDA2822资料手册:引脚说明、参数分析

TDA2822资料手册:引脚说明、参数分析

TJA1050资料数据分析、引脚说明、应用示例介绍

TJA1050资料数据分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍