| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| HY62UF16101CSLF-I-85 | HYNIX |

获取价格 |

Standard SRAM, 64KX16, 85ns, CMOS, PBGA48, FBGA-48 |

|

| HY62UF16101CSLT2-55 | HYNIX |

获取价格 |

Standard SRAM, 64KX16, 55ns, CMOS, PDSO44, 0.400 INCH, TSOP2-44 |

|

| HY62UF16101CSLT2-70 | HYNIX |

获取价格 |

Standard SRAM, 64KX16, 70ns, CMOS, PDSO44, 0.400 INCH, TSOP2-44 |

|

| HY62UF16101CSLT2-85 | HYNIX |

获取价格 |

Standard SRAM, 64KX16, 85ns, CMOS, PDSO44, 0.400 INCH, TSOP2-44 |

|

| HY62UF16101CSLT2-I-55 | HYNIX |

获取价格 |

Standard SRAM, 64KX16, 55ns, CMOS, PDSO44, 0.400 INCH, TSOP2-44 |

|

| HY62UF16101CSLT2-I-70 | HYNIX |

获取价格 |

Standard SRAM, 64KX16, 70ns, CMOS, PDSO44, 0.400 INCH, TSOP2-44 |

|

| HY62UF16101CSLT2-I-85 | HYNIX |

获取价格 |

Standard SRAM, 64KX16, 85ns, CMOS, PDSO44, 0.400 INCH, TSOP2-44 |

|

| HY62UF16101LLM-10I | HYNIX |

获取价格 |

Standard SRAM, 64KX16, 100ns, CMOS, PBGA48, MICRO, BGA-48 |

|

| HY62UF16101LLM-12I | HYNIX |

获取价格 |

Standard SRAM, 64KX16, 120ns, CMOS, PBGA48, MICRO, BGA-48 |

|

| HY62UF16101LLM-85 | HYNIX |

获取价格 |

Standard SRAM, 64KX16, 85ns, CMOS, PBGA48, MICRO, BGA-48 |

|

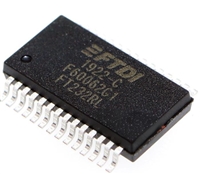

FT232RL资料解读:引脚说明、参数详情、产品特性

FT232RL资料解读:引脚说明、参数详情、产品特性

RC0402FR-07100KL资料解读:电气参数、产品特性

RC0402FR-07100KL资料解读:电气参数、产品特性

RC0603FR-070R数据手册解读:特性、应用与替换型号推荐

RC0603FR-070R数据手册解读:特性、应用与替换型号推荐

ULC1001数据手册解读:产品特性、替换型号推荐

ULC1001数据手册解读:产品特性、替换型号推荐