| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| HCS11MSD | RENESAS | HC/UH SERIES, TRIPLE 3-INPUT AND GATE, CDIP14, WELD SEALED, CERAMIC, DIP-14 |

获取价格 |

|

| HCS11MSK | RENESAS | HC/UH SERIES, TRIPLE 3-INPUT AND GATE, CDFP14, WELD SEALED, CERAMIC, DFP-14 |

获取价格 |

|

| HCS12 | MOTOROLA | HCS12 Document Methodology |

获取价格 |

|

| HCS12 | FREESCALE | HCS12 Microcontrollers |

获取价格 |

|

| HCS1201A | JLWORLD | value applying rated voltage |

获取价格 |

|

| HCS1201AX | JLWORLD | Electro-Magnetic Sound Generators |

获取价格 |

|

pcf8563芯片功能说明、参数分析、引脚说明

pcf8563芯片功能说明、参数分析、引脚说明

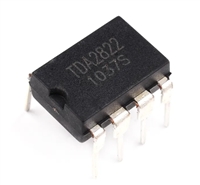

TDA2822资料手册:引脚说明、参数分析

TDA2822资料手册:引脚说明、参数分析

TJA1050资料数据分析、引脚说明、应用示例介绍

TJA1050资料数据分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍