| 生命周期: | Obsolete | 零件包装代码: | LCC |

| 包装说明: | , | 针数: | 84 |

| Reach Compliance Code: | unknown | 风险等级: | 5.84 |

| 技术: | CMOS | uPs/uCs/外围集成电路类型: | MEMORY CONTROLLER, DRAM |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| DP84T22V-25 | TI |

获取价格 |

IC,MEMORY CONTROLLER,CMOS,LDCC,84PIN |

|

| DP8500 | NSC |

获取价格 |

DP8520A/DP8521A/DP8522A microCMOS Programmable 256k/1M/4M Video RAM Controller/Drivers |

|

| DP8500V | TI |

获取价格 |

IC,GRAPHICS PROCESSOR,CMOS,LDCC,68PIN,PLASTIC |

|

| DP8510 | NSC |

获取价格 |

BITBLT PROCESSING UNIT |

|

| DP8510V | NSC |

获取价格 |

IC SPECIALTY MICROPROCESSOR CIRCUIT, PQCC44, PLASTIC, CC-44, Microprocessor IC:Other |

|

| DP8511 | NSC |

获取价格 |

BITBLT PROCESSING UNIT(BPU) |

|

| DP8511V | NSC |

获取价格 |

BITBLT PROCESSING UNIT(BPU) |

|

| DP8511V | TI |

获取价格 |

SPECIALTY MICROPROCESSOR CIRCUIT, PQCC44, PLASTIC, CC-44 |

|

| DP8520A | NSC |

获取价格 |

DP8520A/DP8521A/DP8522A microCMOS Programmable 256k/1M/4M Video RAM Controller/Drivers |

|

| DP8520AV-20 | NSC |

获取价格 |

DP8520A/DP8521A/DP8522A microCMOS Programmable 256k/1M/4M Video RAM Controller/Drivers |

|

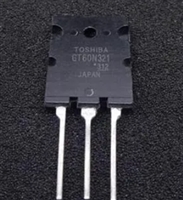

GT60N321资料手册解读:深入了解东芝第四代绝缘栅双极晶体管

GT60N321资料手册解读:深入了解东芝第四代绝缘栅双极晶体管

STS5DNE30L资料手册解读:参数分析、特性与应用

STS5DNE30L资料手册解读:参数分析、特性与应用

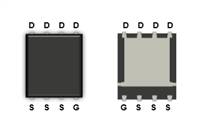

MDU1511资料手册解读:探索这款MOSFET的全面特性

MDU1511资料手册解读:探索这款MOSFET的全面特性

2SB1260资料手册解读:电气参数、产品特性

2SB1260资料手册解读:电气参数、产品特性