| 生命周期: | Obsolete | 零件包装代码: | WAFER |

| 包装说明: | DIE, | Reach Compliance Code: | unknown |

| HTS代码: | 8542.39.00.01 | 风险等级: | 5.7 |

| Is Samacsys: | N | 系列: | LS |

| JESD-30 代码: | X-XUUC-N16 | 逻辑集成电路类型: | D LATCH |

| 位数: | 2 | 功能数量: | 2 |

| 端子数量: | 16 | 最高工作温度: | 70 °C |

| 最低工作温度: | 输出极性: | COMPLEMENTARY | |

| 封装主体材料: | UNSPECIFIED | 封装代码: | DIE |

| 封装形状: | UNSPECIFIED | 封装形式: | UNCASED CHIP |

| 传播延迟(tpd): | 30 ns | 认证状态: | Not Qualified |

| 最大供电电压 (Vsup): | 5.25 V | 最小供电电压 (Vsup): | 4.75 V |

| 标称供电电压 (Vsup): | 5 V | 表面贴装: | YES |

| 技术: | TTL | 温度等级: | COMMERCIAL |

| 端子形式: | NO LEAD | 端子位置: | UPPER |

| 触发器类型: | HIGH LEVEL | Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| DM74LS75J | TI |

获取价格 |

IC,LATCH,SINGLE,4-BIT,LS-TTL,DIP,16PIN,CERAMIC |

|

| DM74LS75J/A+ | TI |

获取价格 |

IC,LATCH,SINGLE,4-BIT,LS-TTL,DIP,16PIN,CERAMIC |

|

| DM74LS75M | TI |

获取价格 |

LS SERIES, DUAL HIGH LEVEL TRIGGERED D LATCH, COMPLEMENTARY OUTPUT, PDSO16, 0.150 INCH, PL |

|

| DM74LS75M | FAIRCHILD |

获取价格 |

Quad Latch |

|

| DM74LS75MX | FAIRCHILD |

获取价格 |

4-Bit D-Type Latch |

|

| DM74LS75N | FAIRCHILD |

获取价格 |

Quad Latch |

|

| DM74LS75N | TI |

获取价格 |

LS SERIES, DUAL HIGH LEVEL TRIGGERED D LATCH, COMPLEMENTARY OUTPUT, PDIP16 |

|

| DM74LS75N/A+ | TI |

获取价格 |

IC,LATCH,SINGLE,4-BIT,LS-TTL,DIP,16PIN,PLASTIC |

|

| DM74LS75N/B+ | TI |

获取价格 |

IC,LATCH,SINGLE,4-BIT,LS-TTL,DIP,16PIN,PLASTIC |

|

| DM74LS76A | TI |

获取价格 |

J-K FLIP-FLOP, PDIP16, DIP-16 |

|

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

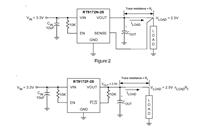

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明

一文带你了解SM8760CA资料:主要参数特征

一文带你了解SM8760CA资料:主要参数特征