| 是否Rohs认证: | 不符合 | 生命周期: | Obsolete |

| 零件包装代码: | QFP | 包装说明: | 14 X 14 MM, CAVITY-UP, CERAMIC, TQFP-64 |

| 针数: | 64 | Reach Compliance Code: | not_compliant |

| 风险等级: | 5.89 | Is Samacsys: | N |

| 地址总线宽度: | 最大数据传输速率: | 80 MBps | |

| 外部数据总线宽度: | JESD-30 代码: | S-CQFP-G64 | |

| JESD-609代码: | e0 | 长度: | 14 mm |

| 湿度敏感等级: | 3 | 端子数量: | 64 |

| 最高工作温度: | 125 °C | 最低工作温度: | -55 °C |

| 封装主体材料: | CERAMIC, METAL-SEALED COFIRED | 封装代码: | QFP |

| 封装等效代码: | QFP64,.66SQ,32 | 封装形状: | SQUARE |

| 封装形式: | FLATPACK | 峰值回流温度(摄氏度): | 225 |

| 电源: | 5 V | 认证状态: | Not Qualified |

| 筛选级别: | 38535Q/M;38534H;883B | 座面最大高度: | 3 mm |

| 子类别: | Bus Controllers | 最大压摆率: | 100 mA |

| 标称供电电压: | 5 V | 表面贴装: | YES |

| 技术: | MOS | 温度等级: | MILITARY |

| 端子面层: | Tin/Lead (Sn/Pb) | 端子形式: | GULL WING |

| 端子节距: | 0.8 mm | 端子位置: | QUAD |

| 处于峰值回流温度下的最长时间: | 30 | 宽度: | 14 mm |

| uPs/uCs/外围集成电路类型: | BUS CONTROLLER, VME | Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| CY7C960-UMB | CYPRESS | Low Cost VMEbus Interface Controller Family |

获取价格 |

|

| CY7C961 | CYPRESS | Low Cost VMEbus Interface Controller Family |

获取价格 |

|

| CY7C961-AC | ETC | VME/VMS/VXI/VSB Bus Interface/Controller |

获取价格 |

|

| CY7C961-NC | CYPRESS | Low Cost VMEbus Interface Controller Family |

获取价格 |

|

| CY7C964 | CYPRESS | Bus Interface Logic Circuit |

获取价格 |

|

| CY7C964A | CYPRESS | Bus Interface Logic Circuit |

获取价格 |

|

IRF3205功率MOSFET:资料手册参数分析

IRF3205功率MOSFET:资料手册参数分析

MC34063开关稳压器:全面参数解析与设计指南

MC34063开关稳压器:全面参数解析与设计指南

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

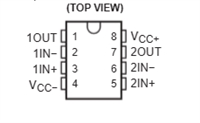

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析