半导体行业再迎重磅合作!6月16日,Cadence楷登电子宣布与三星晶圆代工签署新多年期IP协议,双方将共同推进SF2P等先进制程节点的内存与接口IP开发。这场强强联合不仅加速了2nm工艺的商用进程,更在台积电独占鳌头的先进制程领域投下变量。这场合作将如何重塑半导体产业格局?

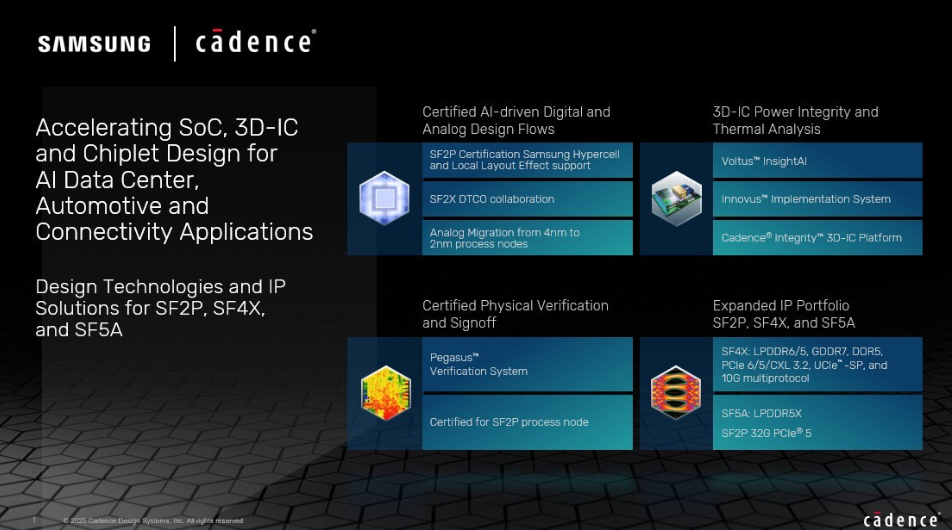

根据协议,Cadence将为三星SF4X、SF5A和SF2P三大制程节点提供关键IP支持。在SF4X节点,LPDDR6/5x-14.4G、GDDR7-36G等高速内存接口技术将得到优化;SF5A节点则专注于汽车级LPDDR5X-8533 PHY IP开发;而最受关注的SF2P节点将集成32G PCIe5.0 PHY技术。值得注意的是,双方已完成模拟电路IP从4nm向2nm的迁移,这为三星2nm量产扫清了技术障碍。

这一合作恰逢三星2nm芯片Exynos2600进入原型量产的关键阶段。该芯片采用第三代GAA晶体管技术,实测显示比3nm芯片功耗降低25%,性能提升12%,芯片面积缩小5%。但30%的良率仍是致命短板,每10片晶圆仅3片合格,导致特斯拉等客户转向台积电3nm方案。为扭转局面,三星祭出组合拳:代工报价比台积电低10%-15%,提供免费技术支持,甚至推出"风险共担合同"——若良率未达标,三星将承担部分损失。

Cadence的IP技术注入被视为三星提升良率的重要筹码。双方在2nm节点的设计优化和认证支持,直接对标台积电60%的初期良率。特别是在背面供电网络(BSPDN)技术上,Cadence的解决方案有望解决GAA晶体管的多阈值电压挑战。这项技术对三星SF2系列制程至关重要:SF2P面向低功耗移动设备,SF2X/SF2Z主打AI与高性能计算,SF2A则专注车规级芯片。

晶圆代工战场已进入白热化阶段。台积电2nm试产良率超60%,计划2025年量产;日本Rapidus联手IBM,预计2025年4月启动2nm试产。三星凭借与Cadence的深度绑定,试图在技术迭代速度上实现弯道超车。但行业分析师指出,真正的较量在于良率稳定性——高通、英伟达等大客户要求良率稳定在60%以上才会下单,这正是三星当前40%良率与目标70%之间的生死线。

这场合作的影响将远超技术层面。若三星能在年底前将2nm良率提升至50%,Galaxy S26系列或将采用Exynos2600与骁龙8 Elite 2的双芯片策略;反之可能全系改用台积电方案。更深远的是,Cadence的IP技术扩散将加速2nm生态成熟,可能改变目前台积电独占苹果、高通等头部客户的局面。

半导体产业的竞赛从来不只是制程数字的游戏。Cadence与三星这场跨越多个技术节点的合作,正在改写先进制程的经济公式——当IP生态、良率控制与成本优化形成合力,2nm时代的产业格局或将迎来新一轮洗牌。随着2025年量产窗口的临近,这场关乎万亿市场的技术博弈已进入倒计时。

浙公网安备 33010502006866号

浙公网安备 33010502006866号