在全球节能减排的大趋势下,降低电子设备的待机功耗已成为技术攻坚的核心课题。AC-DC电源作为电力转换的关键环节,其待机功耗的高低直接影响着能源浪费水平。本文将深入解析如何通过初级侧调节反激式拓扑、智能控制策略及器件优化,实现待机功率低于5mW甚至趋近于零的技术路径。

反激式拓扑:低功耗设计的基石

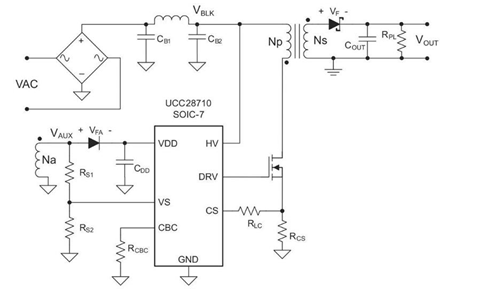

反激式拓扑凭借其结构简单、成本低廉的显著优势,成为了低功耗离线电源的首选方案。在传统设计中,光耦器件被用于次级侧电压反馈,然而其功耗与稳定性问题逐渐凸显出来。现代准谐振(QR)反激式控制器则通过初级侧调节技术,彻底摆脱了对光耦的依赖。它利用变压器偏置绕组的磁反馈形成闭环控制,仅需电阻分压网络就能够精准调节输出电压。以德州仪器UCC28710控制器为例(如图1所示),它通过检测谐振谷值电压实现软开关,可将开关损耗降低40%以上。

图1:基于UCC28710的初级侧稳压反激式架构

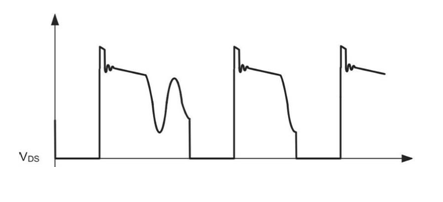

准谐振技术的核心在于巧妙利用电路寄生参数(初级电感与开关节点电容)产生的谐振特性。如图2所示,当次级电流归零后,控制器会在谐振电压谷底触发MOSFET导通,使开关节点电压从400V降至50V以下,从而显著减少开关过程中的能量损耗。这种“谷底开关”机制,能够将转换效率提升至88%以上。

图2:谷底开关显著降低电压应力(Vds为MOSFET漏源电压)

待机功耗构成与优化路径

要实现极低的待机功耗,需要系统化地解决三大能量损耗源:

周期性能量损耗:每个开关周期从输入源获取的能量(E_cycle)直接决定了待机功耗水平。其计算公式为:,其中,为MOSFET输出电容,为母线电压,为开关频率。通过将开关频率降至10kHz以下,UCC28710在空载时的周期损耗可控制在3mW以内。不过,低频运行会使瞬态响应变差,当负载突变时,控制器需要长达100ms才能检测到电压波动。

启动电路革新:传统电阻启动方案在230VAC输入时会产生超过200mW的损耗,成为待机功耗的主要短板。革新方案采用耗尽型MOSFET构建有源启动电路。上电初期,FET导通为控制器供电;输出电压建立后,FET被关断。该设计使启动损耗从毫瓦级降至微瓦级,配合UCC28710的自适应供电系统,整体待机损耗可减少60%。

缓冲网络与寄生参数治理:

TVS缓冲替代RCD网络:瞬态电压抑制二极管(TVS)在电压超过箝位值前几乎无损耗,较传统RCD方案效率可提升5%。

超快恢复二极管选择:反向恢复时间<35ns的二极管可减少开关节点震荡损耗。

寄生电容压缩:通过优化PCB布局与选用低MOSFET(如InfineonIPA60R280P7),可将开关节点总电容控制在150pF以内。

零待机功耗的终极方案

要突破5mW待机功耗壁垒,需要颠覆性的技术创新。德州仪器推出的UCC28730+UCC24650芯片组,通过“超低频运行+智能唤醒”机制实现了革命性突破:

关键技术突破:

32Hz超低频模式:空载时开关频率降至32Hz,周期损耗仅0.8mW。

跨隔离栅唤醒技术:次级侧UCC24650实时监测输出电压,当负载接入导致电压下降3%时,通过变压器耦合发送唤醒信号。

三脉冲加速响应:初级侧控制器收到信号后,立即以65kHz频率发送三个脉冲,在10ms内恢复稳压输出。

性能对比:

工程实践挑战与对策

在实际设计中,工程师需要平衡多项矛盾因素:

瞬态响应与功耗的博弈:

预负载策略:在输出端添加10kΩ电阻(损耗5mW)可改善动态性能,但会增加待机功耗。

自适应频率调制:根据负载情况动态调整开关频率,轻载时运行于10kHz,重载时升至130kHz。

器件选型准则:

MOSFET:优选<100pF、<0.3Ω的CoolMOS(如STF10N65M5)。

变压器:采用TDKPC40材质,漏感控制在2%以内。

输出二极管:超快恢复类型(如ONSemiMUR160),反向恢复时间<50ns。

热管理设计:在85℃环境温度下,需确保启动MOSFET结温<110℃;使用3M导热胶将控制器与PCB铜箔区域紧密贴合,热阻降至15℃/W。

行业应用与未来展望

目前,该技术已在智能手机充电器(如小米120W快充)、智能家居网关等场景实现商用。欧盟ErP指令要求2026年后所有外置电源待机功耗<5mW,这将推动相关方案快速普及。未来,随着GaN器件与数字控制技术的融合,AC-DC电源有望在保持零待机损耗的同时,将功率密度提升至30W/in³,为能源革命注入新的动力。

浙公网安备 33010502006866号

浙公网安备 33010502006866号