在半导体领域,研究半导体电荷捕获和退化行为至关重要。传统上,交流或脉冲应力是对典型应力测试的有益补充。以NBTI(负偏置温度不稳定性)和TDDB(随时间变化的介电击穿)试验为例,其应力/测量循环中所施加的应力电压通常为直流信号,因其更易于映射到器件模型。然而,结合脉冲应力测试能提供额外数据,有助于更好地理解依赖频率电路的器件性能。

传统的直流应力和测量技术广泛用于表征CMOS晶体管的可靠性,像沟道热载流子注入(HCI)和时间依赖性介电击穿(TDDB)引起的退化。但随着新的可靠性测试发展,如金属氧化物半导体场效应晶体管(PMOSFET)和高κ材料器件中的电荷捕获,可靠性测试的性质也发生了变化。这些现象对评估新过程的可靠性影响重大。而且,人们对评估实际运行中多个设备动态开关电路的可靠性愈发关注。

新材料和结构的应用使动态可靠性测试受到更多重视。在可靠性测试器件中引入脉冲或交流应力,以及在测量过程中引入脉冲来表征应力引起的界面退化成为新趋势。研究表明,电压应力导致的界面退化或界面陷阱密度增加,是引发HCI、NBTI等器件可靠性问题以及高κ材料可靠性问题的关键因素。在现有的直流表征测试中添加界面陷阱监测测试,对理解这些新的可靠性问题十分有用。本白皮书将探讨先进CMOS技术可靠性测试中常用的电荷泵和交流应力技术。

这里提到的“交流压力”用词不太准确,实际应用中的交流应力是一列方形或梯形电压脉冲,为便于表述,本文使用“脉冲应力”这一术语。

脉冲表征-电荷泵

电荷泵(CP)和同时进行的C-V(高频和准静态C-V的结合)测量是表征MOS器件中界面陷阱态密度的常用方法。然而,随着晶体管尺寸缩小、栅氧化物变薄,准静态C-V对于小于3-4nm的氧化物不再适用,因此同时C-V不适合新的高κ材料的界面陷阱表征。

CP是理解栅叠加行为的有效技术,随着高κ薄膜在晶体管栅中的应用增多,其重要性日益凸显。CP可表征界面和电荷捕获现象,通过CP结果的变化能确定典型可靠性测试方法(如热载流子注入(HCI)、负偏置温度不稳定性(NBTI)和随时间变化的介电击穿(TDDB))所引起的退化量。

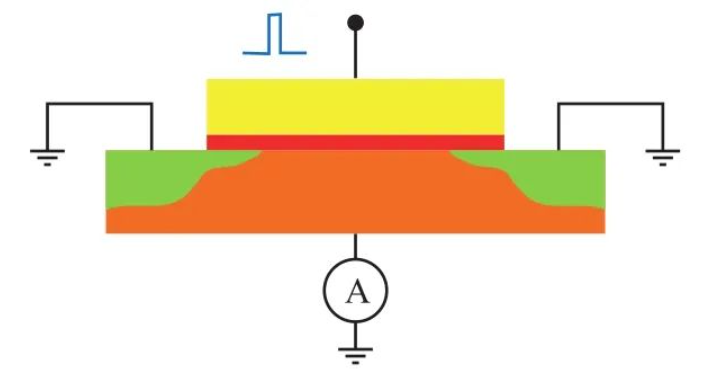

图1:电荷泵测量示意图。晶体管的源极和漏极连接到地面,而栅极以固定的频率和振幅进行脉冲

图1展示了与被测设备(DUT)的连接。基本的CP技术是在对晶体管的栅极施加固定幅度、上升时间、下降时间和频率的电压脉冲序列时,测量基极电流。在此测试中,漏极、源连接到地面,衬底通过源测量单元(SMU)连接到地面,用于测量通过栅极的电流(Icp)。

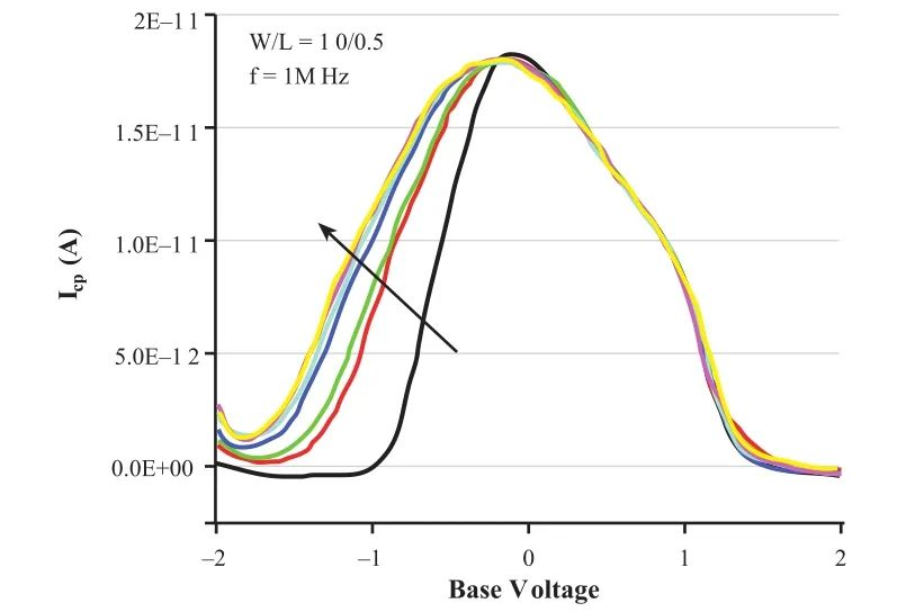

常见的CP技术有电压基极扫描和幅值扫描。电压基极电平扫描中,周期(脉冲宽度)和电压振幅固定,扫描脉冲基极电压,在每个电压下测量体电流并绘制基本电压(ICPvsVbase),如图2a所示。

图2用于电荷泵送的两种扫描类型:a)基极电压扫描b)脉冲幅度扫描

电压幅度扫描则是固定基本电压和周期(脉冲频率),每个扫描步骤的电压振幅变化。所获数据与电压基极扫描相似,但此时是电荷泵电流与电压幅度(ICPvs电压幅度)。这些测量也可在多个频率(周期)上执行,以获得界面陷阱的频率响应。

对于高κ材料结构,CP技术可将被捕获的电荷(Nit)量化。在硅基板/界面层以外的捕获电荷也能被感知到。图2a为基底电压扫描的特征ICP曲线,图2b为电压幅值扫描的特征ICP曲线。

CP技术还可用于表征界面阱形成的初始阶段。图3显示了使用1MHz频率的“新”CP测量(即以前未测试过的MOSFET)。暗态电流是初始的CP测量值,较浅的曲线表示随后的测量结果。可以看到,在较低电压下,ICP曲线的形状和大小都发生了变化。多次测量后,随着效果饱和,变化趋势停止。曲线形状的变化表明,CP测量所施加的电应力导致了界面陷阱的形成,这意味着使用脉冲测量CP能有效对器件施加压力并引起一定退化。脉冲应力下的退化对理解偏置温度不稳定性(BTI)和TDDB有重要补充作用。

图3.“新”器件上的电荷泵测量所引起的应力效应

BTI和TDDB的脉冲应力

BTI(包括NBTI和PBTI)和TDDB的测试方法类似,都包括应力和测量两个间隔,用高电压施加压力,交替定期测量以确定退化量。NBTI和TDDB通常在高温下进行,以加速退化、缩短测试时间,测试时间可能从一小时到两周不等。

近年来,NBTI在PMOSFET测试中成为重要的可靠性问题。NBTI是栅极-通道界面变化导致PMOS器件性能退化的现象,通常表现为晶体管阈值电压(VT)增加和漏极电流(ID)退化。在老化或场效应场景下,这种退化会降低产量。NBTI测试有最近发布的行业标准。NBTI和传统的HCI测试的最大区别在于,NBTI测试中,消除应力时,应力诱导的退化会出现弛豫。

这种弛豫给传统的应力和测量技术带来挑战。因为在测量间隔中,当器件未施加电压时,应力间隔和测量间隔有过渡时间,此时部分压力消除,仪器“看到”的器件性能会高估器件寿命,因为退化效应减少。而且,直流应力电压不能准确表示器件在真实电路中承受的应力,因为多数器件在不工作时会经历弛豫,所以直流应力技术可能低估晶体管在真实电路中的寿命。随着新技术的可靠性利润率缩小,评估晶体管使用寿命的成本可能增加。

除了弛豫这种动态可靠性行为,高κ栅材料的晶体管中还存在电荷捕获现象。这是因为CMOS工艺中沉积高κ材料的过程不成熟,与二氧化硅门工艺相比,薄膜中有大量陷阱中心。栅极打开时,电荷可暂时捕获在栅极中,随时间改变晶体管性能,捕获的电荷会改变晶体管的阈值电压。根据栅极质量和捕获条件,捕获电荷可能需要几十毫秒到毫秒。

高κ栅极内的电荷分布会影响电场分布,从而改变高κ栅极的可靠性行为。同时,在较低栅极电压下去除电荷时,也存在类似的弛豫效应。弛豫会导致对设备寿命的不准确估计,因为它强烈依赖时间,且在测试环境中,应力测量的过渡时间和弛豫时间通常难以很好控制。

新的可靠性现象的动态特性要求用脉冲应力来模拟电路内器件的性能。不同电路和电路拓扑工作频率不同,可能需要与频率相关的寿命提取来建立基于频率寿命的模型。在这些应用中,脉冲应力比直流应力技术更具优势。脉冲应力对器件施加动态信号,更接近频率相关的电路行为。在脉冲应力期间,应力中断,退化部分恢复,可恢复器件寿命。应力产生的界面陷阱,在应力关闭期间会部分退火或修复。由于这种恢复(或自退火)行为,可靠性工程师和科学家使用脉冲应力技术来更好地评估器件寿命,使其更适用于电路内或产品内的条件。

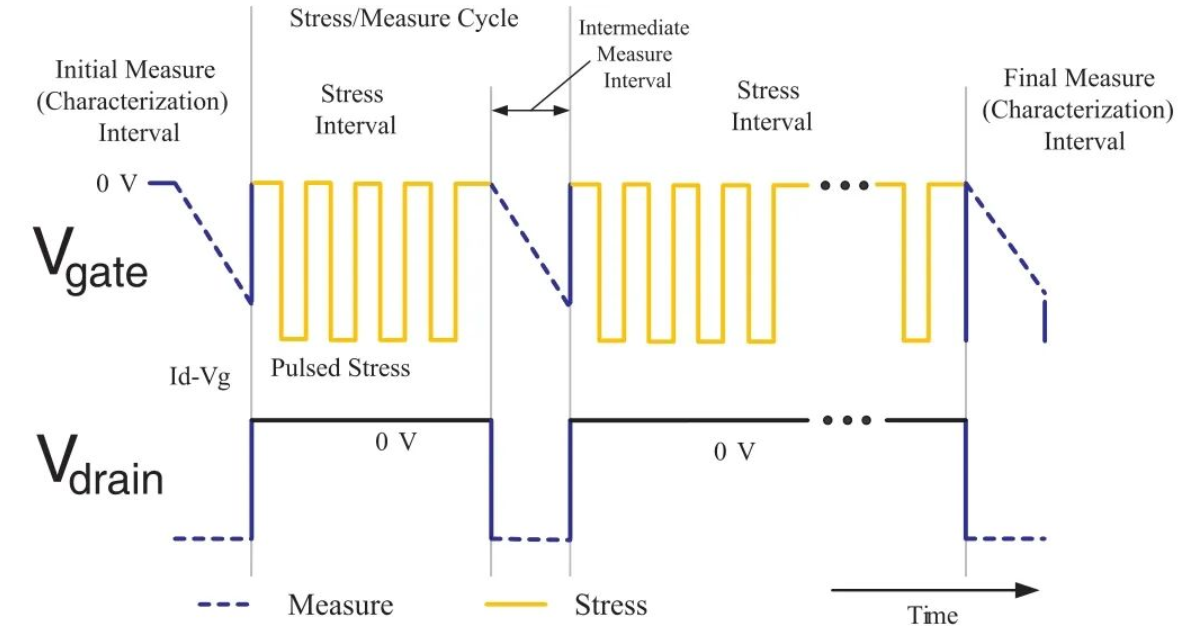

图4a

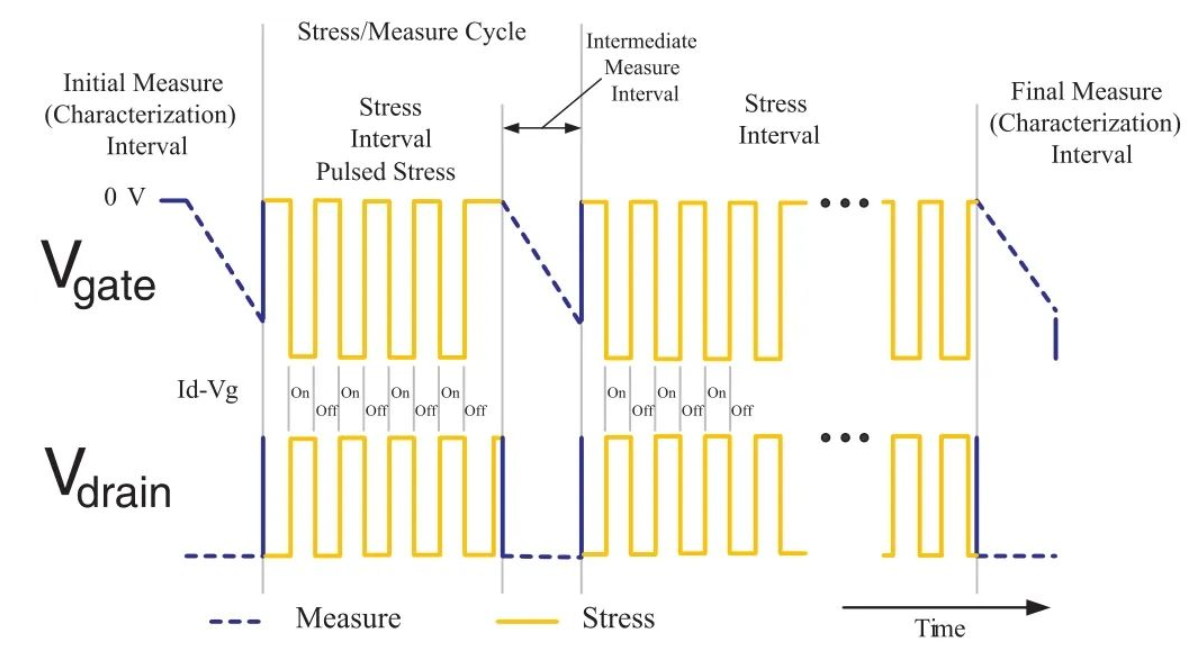

图4.NBTI应力/测量图,显示了两种不同的脉冲应力方法:a)使用传统栅极和漏极电压的动态NBTI(DNBTI)b)DNBTI模拟逆变器条件,漏极电压与栅极电压处于相反的相位

通过周期性应力模拟器件在电路中的应力,脉冲应力本质上是短的直流应力,被无应力时间中断(如图4)。对于NBTI,应力脉冲间的非应力部分可使退化部分恢复,这对确定和模拟器件使用寿命行为很重要。不过,部分恢复的机制还未完全明确,且会因器件的结构、尺寸和材料组合而异。图4展示了两种脉冲应力示例,图4a中NBTI的脉冲应力,漏极电压在应力间隔期间保持0V;图4b中除栅极电压外,漏极电压也脉冲,用于模拟逆变电路中单个器件的性能。图4b中栅极和漏极都受压力,器件退化过程中同时存在NBTI和HCI。一般来说,脉冲应力技术产生的退化更少,器件寿命更长。

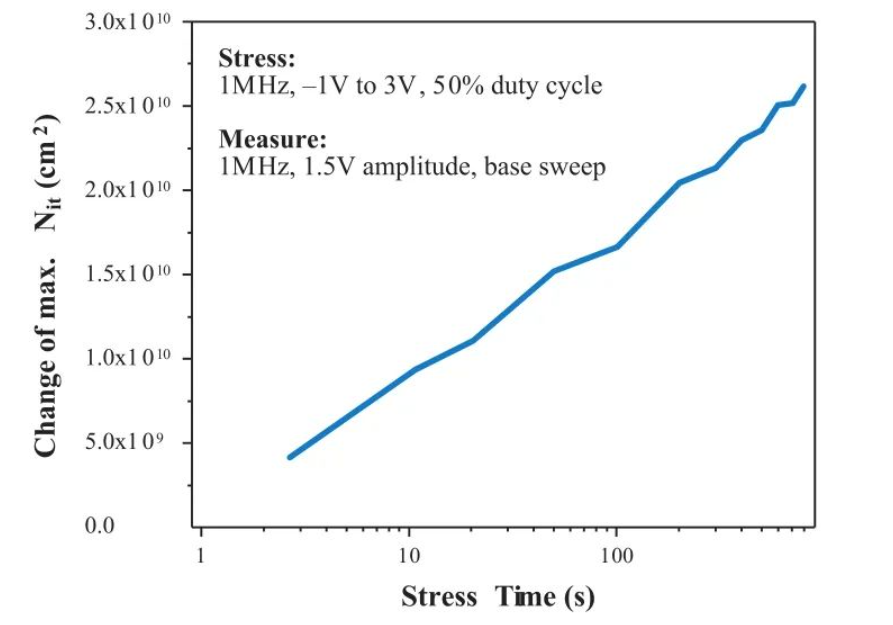

图5.由于脉冲应力而导致的Nit退化

对于NBTI,脉冲应力技术用于研究单个器件以及数字电路的动态行为。图5显示了不同脉冲应力持续时间导致的Nit增加,结合了图4a的应力方法和图2a的周期性CP测量值。

除了BTI,TDDB在静态和动态故障状态中的作用也能通过脉冲应力更好地理解。在TDDB测试期间监测SILC(应力引发的泄漏电流)时,应力/测量图类似于图4a,但Vdrain保持恒定非零电压,以便在应力期间读取Id。

结论

脉冲电压为研究高κ薄膜的固有材料、界面和可靠性性能以及基于这些新薄膜的器件提供了关键能力。脉冲电压同时测量直流电流是电荷测量的基础,对测量固有电荷捕获具有重要价值。与直流或脉冲应力结合使用,CP可研究电荷捕获以及高κ-Si界面和高κ薄膜内的新电荷产生。脉冲应力还提供了一种能更好模拟电路内器件实际应力的方法,对BTI、TDDB和HCI等各种器件的可靠性测试都很有用。此外,脉冲应力补充了传统的直流技术,能更好地表征器件的可靠性行为。

浙公网安备 33010502006866号

浙公网安备 33010502006866号