在当今科技飞速发展的时代,半导体产业作为推动电子信息领域进步的核心力量,其工艺技术的发展一直是行业关注的焦点。近年来,半导体工艺的 “军备竞赛” 正逐渐转向 High - NA EUV(高数值孔径极紫外光刻)技术,而 2nm 制程仅仅是这场新竞赛的起点。

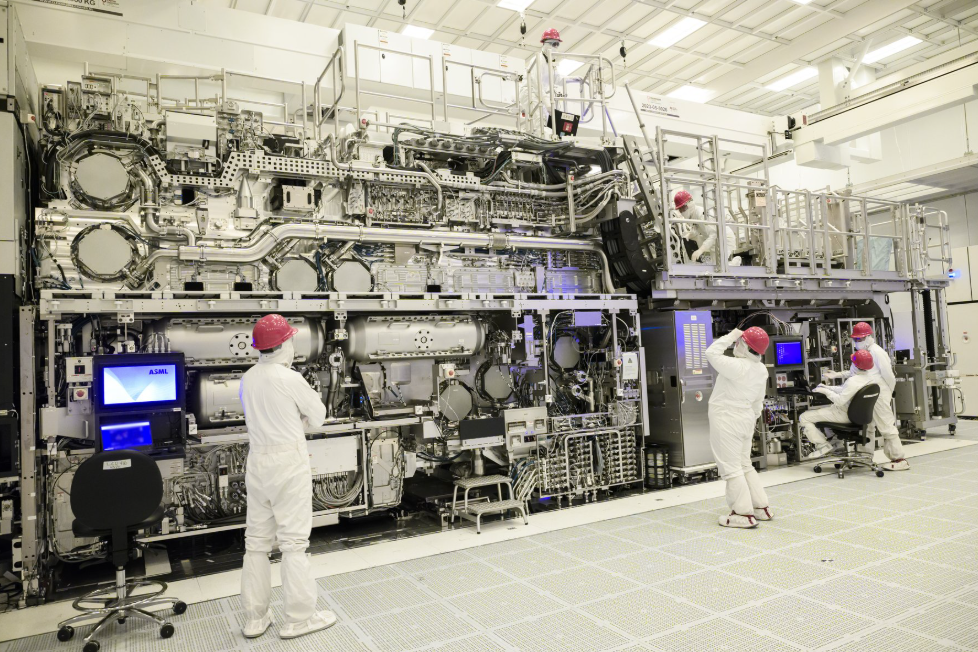

光刻技术在半导体芯片制造过程中扮演着至关重要的角色,它决定了芯片上电路图案的精度和复杂度。传统的 EUV(极紫外光刻)技术已经在先进制程芯片制造中得到了广泛应用,但随着芯片制程不断向更小尺寸迈进,传统 EUV 技术的局限性逐渐显现。High - NA EUV 技术应运而生,它通过提高光刻系统的数值孔径,能够实现更高的分辨率和更小的线宽,从而满足 2nm 及以下制程芯片制造的需求。

High - NA EUV 技术的原理基于光学成像的基本理论。数值孔径(NA)是衡量光学系统聚光能力和分辨率的重要参数,提高数值孔径可以使光刻系统在曝光过程中更精确地将掩膜版上的图案投影到晶圆上,从而实现更小尺寸的电路图案。与传统 EUV 技术相比,High - NA EUV 技术的数值孔径更大,能够突破传统光刻技术的分辨率极限,为制造更先进的芯片提供了可能。

目前,2nm 制程已经成为半导体产业的一个重要里程碑。2nm 芯片在性能、功耗和集成度方面都具有显著优势,能够满足人工智能、大数据、5G 通信等新兴领域对高性能芯片的需求。然而,要实现 2nm 及以下制程的大规模量产,面临着诸多技术挑战。其中,光刻技术是关键的瓶颈之一。传统 EUV 技术在 2nm 制程下已经难以满足芯片制造的精度要求,而 High - NA EUV 技术则成为解决这一问题的关键。

2nm 芯片的制造流程极其复杂,涉及多个环节。从晶圆的制备到光刻、蚀刻、掺杂等工艺,每一个环节都需要高精度的控制和先进的技术支持。在光刻环节,High - NA EUV 技术的应用可以使芯片上的电路图案更加精细,从而提高芯片的性能和集成度。例如,在制造高性能处理器时,更小的电路图案可以容纳更多的晶体管,从而提高处理器的运算速度和处理能力。

High - NA EUV 技术的发展也面临着一系列挑战。首先,该技术的研发成本极高,需要大量的资金和人力投入。其次,High - NA EUV 设备的制造难度大,对光学元件的精度和稳定性要求极高。此外,High - NA EUV 技术在实际应用中还需要解决一系列工艺问题,如光刻胶的性能、曝光剂量的控制等。

尽管面临诸多挑战,但 High - NA EUV 技术在半导体产业的应用前景依然广阔。随着人工智能、物联网、自动驾驶等新兴技术的快速发展,对高性能芯片的需求将不断增加。High - NA EUV 技术能够为制造更先进的芯片提供技术支持,从而推动这些新兴技术的发展。例如,在人工智能领域,高性能芯片是实现深度学习和神经网络计算的关键,High - NA EUV 技术制造的芯片可以提高人工智能系统的运算速度和处理能力,从而推动人工智能技术的发展。

对于半导体企业来说,掌握 High - NA EUV 技术将成为在未来市场竞争中占据优势的关键。目前,全球主要的半导体企业如台积电、三星等都在积极投入 High - NA EUV 技术的研发和应用。台积电已经宣布将在 2nm 制程中采用 High - NA EUV 技术,以提高芯片的性能和竞争力。三星也在加大对 High - NA EUV 技术的研发投入,试图在 2nm 及以下制程领域取得突破。

半导体工艺的 “军备竞赛” 转向 High - NA EUV 技术是产业发展的必然趋势。2nm 制程仅仅是这场新竞赛的起点,未来随着 High - NA EUV 技术的不断发展和成熟,半导体芯片的制程将不断向更小尺寸迈进,为科技的发展带来更多的可能性。在这场激烈的竞争中,半导体企业需要不断加大研发投入,提高技术水平,以适应市场的需求和产业的发展。同时,政府和行业组织也需要加强对半导体产业的支持和引导,推动 High - NA EUV 技术的研发和应用,促进半导体产业的健康发展。

896

896

浙公网安备 33010502006866号

浙公网安备 33010502006866号