在众多电子系统中,常常需要通过控制线或者在施加输入电源时来实现电源的启用和禁用操作。虽然小型微控制器(MCU)能够实现这一启用/禁用功能,然而,使用MCU需要编写、维护和烧录代码,这无疑增加了开发和维护的成本与复杂度。此外,许多采用片上系统(SoC)的设计,其芯片内部本身就集成了一个MCU,此时再额外添加一个MCU就显得多余了。并且,SoC中的MCU功耗相对较高,难以保持始终开启以提供稳定的启用控制器功能。

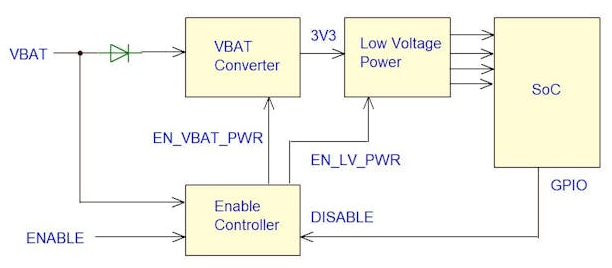

本文将深入探讨一种低成本、低功耗的使能控制器硬件解决方案,该方案巧妙地结合了低压差线性稳压器(LDO)和可编程逻辑器件(PLD),仅消耗微安级的电流。其中,PLD预先编程了实现使能控制器决策功能所需的逻辑。图1展示了该建议解决方案,其电源通常应用于为SoC供电的汽车系统。

图1.说明SoC、电源和使能控制器的基本系统图。

启用控制器解决方案

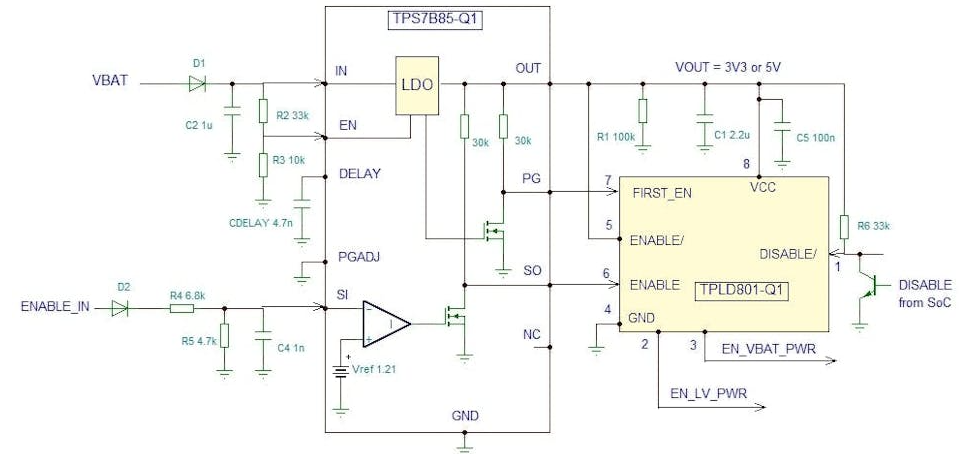

该解决方案采用了TPS7B85-Q1电池断续LDO1和TPLD801-Q1PLD2,如图2所示。TPS7B85-Q1中的多项功能在本应用中具有重要价值:

基本LDO功能:能够从高达40V的电池电压(VBAT)提供固定的3.3V或5V输出电压(VOUT),此VOUT为TPLD801-Q1供电。

具有引脚可编程延迟的电源就绪(PG)输出:当施加VBAT时,LDO上电。当LDOVOUT达到稳压状态后,PG在DELAY引脚上的电容器编程的延迟后变为高电平。TPLD801-Q1利用上升的PG信号来检测和锁存VBAT(FIRST_EN)的初始应用,从而启用系统。

非专用SENSE比较器:如果其感应输入引脚(SI引脚)分别高于或低于1.21V内部电压基准(VREF),则提供逻辑高电平或低电平检测输出(SO引脚)。SI引脚的最大电压为40V,无论LDOVIN是否通电。为了阻断负电压,可以使用二极管D2。该比较器用于测试ENABLE_IN信号的幅度是否高于某个电压阈值,若高于该阈值,则允许信号传递到TPLD801-Q1的使能输入。此电压阈值可通过R4和R5进行调节。

精密使能(EN)引脚:精密使能功能(与逻辑电平使能相反)未在TPS7B85-Q1数据表中详细记录,但EN引脚连接到具有1.32VVREF阈值(上升)和100mV迟滞的比较器。它允许使用从VBAT到EN再到接地的电阻分压器(R2,R3)来设置精确的VBAT启动电压。使用精密使能可确保LDO的输出不会随着VBAT(具有未知的斜坡速率)而斜坡上升,而是等到VBAT高于设定的启动电压后再打开LDO。在这种情况下,VOUT在大约240μs内上升,与VBAT斜坡速率无关。从所示的电阻值来看,LDO的VBAT启动电压约为6.5V,但可通过R2和R3进行调节。需要注意的是,VOUT的斜坡速率很重要,因为TPLD801-Q1的最大(最慢)允许VCC斜坡速率为0.25V/ms。

图2.这是使能控制器的原理图。

泄放电阻R1在掉电期间对LDO(C1)的输出电容器进行放电。TPS7B85-Q1的PG和SO引脚上具有30kΩ内部上拉电阻器。PG延迟的长度可根据实际需求进行选择,例如,CDELAY=4.7nF时的延迟约为4ms(如图2所示)。

TPLD801-Q1的一些设计说明

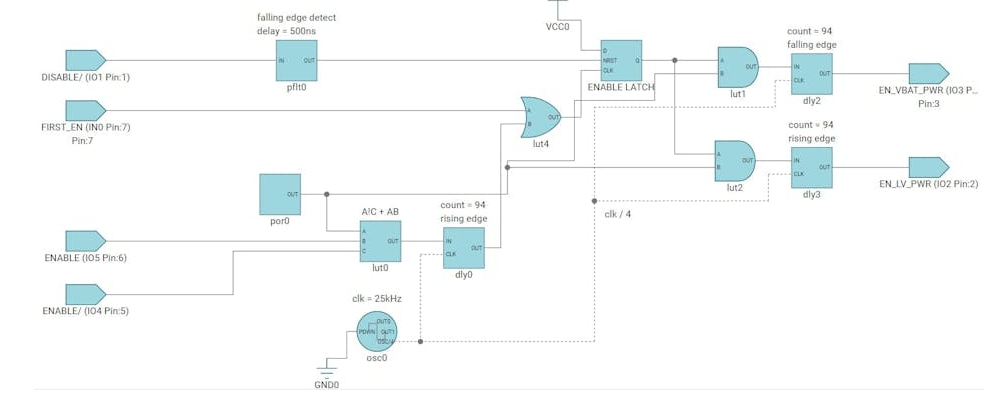

TPLD801-Q1是一款符合汽车标准的PLD,它集成了触发器、计数器、延迟、逻辑门和25kHz或2MHz振荡器等逻辑模块,以及分频器和流水线延迟。TI的InterConnectStudio设计工具可以以图形方式对逻辑设计进行设计和仿真。

用户还可以使用TPLD801评估模块和TPLD编程器套件将逻辑设计永久编程到一次性可编程存储器中,或将设计临时编程到易失性寄存器中。

TPLD801-Q1逻辑设计的核心是一个配置为锁存器(ENABLELATCH)的D型触发器,因此上升时钟沿会锁存一个逻辑高电平输出。只有复位输入可以重置该锁存器。锁存器输出进入两条单独的延迟线,每条延迟线设置为大约15ms。当锁存器输出变为高电平时,EN_VBAT_PWR信号立即变为高电平并启用前端电源。

为了给前端电源留出上电时间,EN_LV_PWR信号在大约15毫秒后变为高电平,并使能为SoC和系统其余部分供电的电源。

可以通过两种方式为ENABLELATCH提供上升沿的时钟:

在第一个使能事件中,在LDO的PG输出上产生一个上升沿。

使用ENABLE信号从TPS7B85-Q1的SO输出传递到PLD,并且PLD测量该信号的持续时间比预编程的持续时间长。或者,如果需要不同的应用程序,也可以使用反向ENABLE/信号;但如果不使用,它就会被拉高。

在第二种情况下,为了抑制杂散噪声信号,PLD通过延迟线来测量输入的ENABLE信号是否足够长,该延迟线由PLD的内部25kHz除频振荡器计时。25kHz振荡器的功耗非常低,仅为8.2μA。

延迟线计数94的总延迟约为15毫秒,但用户可以根据应用程序的要求将此时间设置为不同的持续时间。如果在此延迟期间和之后输入的ENABLE信号仍然存在,则延迟线的输出变为高电平,这会为ENABLELATCH的时钟提供上升沿并锁存一个逻辑高电平。如果输入的ENABLE信号在整个时间内都不存在,则延迟计数器将重置,并且不会发生锁存器的上升沿。

当电子控制单元需要断电时,SoC的MCU通过通用输入/输出发出上升沿。该DISABLE信号连接到图1所示的漏极开路晶体管,并下拉PLD的DISABLE/引脚以重置ENABLELATCH。ENABLELATCH复位后,EN_LV_PWR输出立即变为低电平;大约15ms后,EN_VBAT_PWR输出变为低电平。

这个15毫秒的延迟使低压电源轨能够在前端电源被禁用之前按照SoC要求的正确顺序进行降序。EN_VBAT_PWR和EN_LV_PWR上升或下降之间的延迟时间可以通过更改延迟线的数量来配置。

选择PLD输入作为施密特触发器输入,为驱动到它们的逻辑信号需要多快转换提供了一定的余地。两个使能输出信号配置为推挽式。(如果使用开漏,则此配置会在上电时产生毛刺,因为在TPLD801-Q1的一次性可编程存储器OTP加载并将输出配置为开漏之前,开漏输出被上拉电阻器暂时拉高。即使使用推挽式,在OTP存储器加载之前,输出也是高阻抗的;因此,可能需要外部下拉电阻器。图3显示了整体PLD设计。

图3.此图显示了TPLD801-Q1的内部结构。

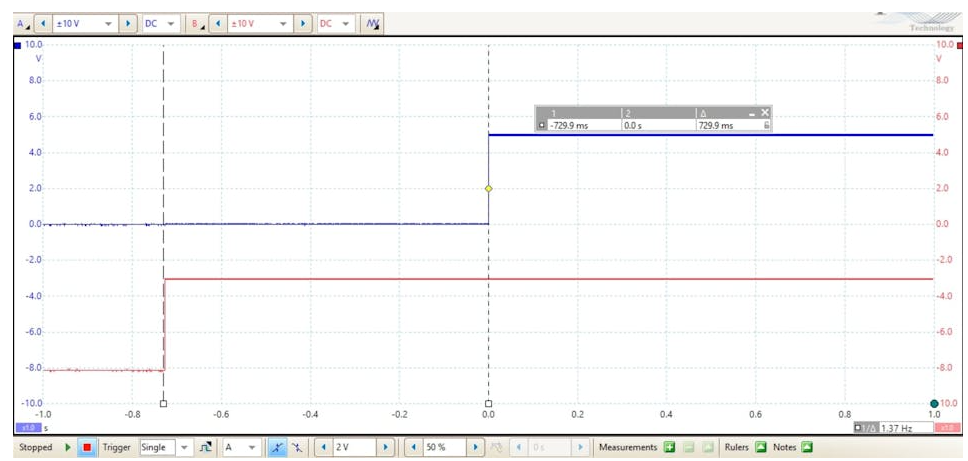

PLD/LDO组合的基准测试结果

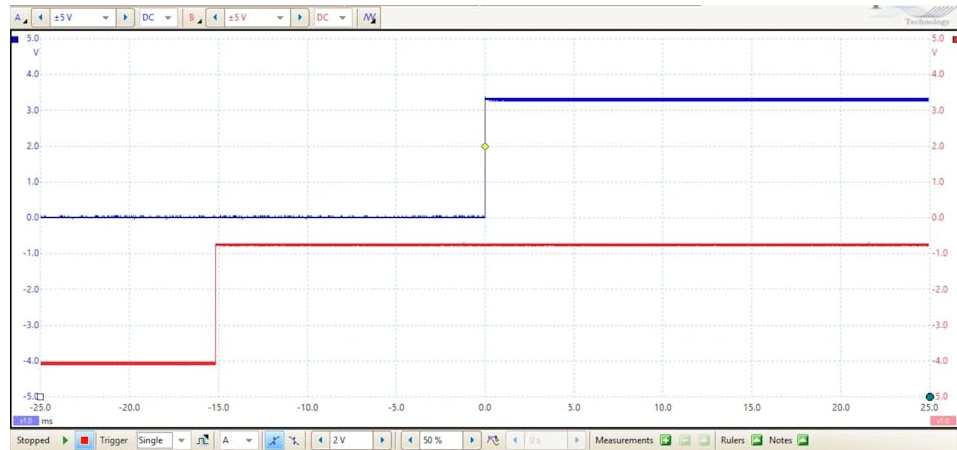

图4显示了施加到使能控制器的18VENABLE_IN信号,该信号的幅度足以使TPS7B85-Q1比较器将其传递到PLD。该信号还具有足够的持续时间,以便PLD进行验证检测。ENABLELATCH响应此ENABLE_IN信号而锁定为高电平,即使ENABLE_IN被切换,它也保持高电平。

图4.将18VENABLE_IN信号施加到使能控制器,该信号肯定具有允许TPS7B85-Q1比较器将其传递到PLD的幅度。用于18VENABLE_IN信号的TPS7B85-Q1SI引脚电压以红色显示,ENABLELATCH内部PLD电压以蓝色显示。

在另一个极端情况下,可以成功地对低幅度的3.4V信号重复此测试。或者,也可以对持续时间短、振幅低的ENABLE_IN信号重复测试,或者两者兼而有之,这些信号的持续时间或振幅不足以触发ENABLELATCH为高电平。

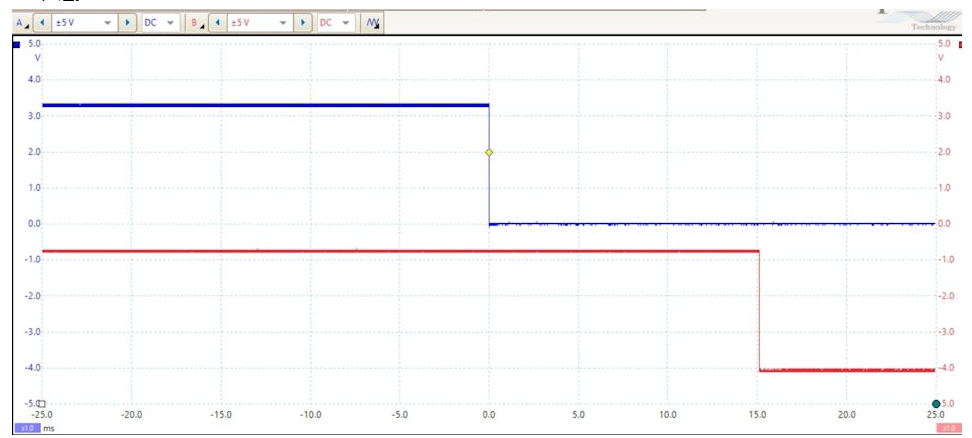

图5显示了首次将输入电源施加到LDO时的电路行为。当LDO调节时,PG引脚变为高电平,经过延迟(由CDELAY设置)后,PLD检测到第一个上电事件,并且ENABLELATCH锁存为高电平。(此测试使用评估板的默认1μFCDELAY电容器,其延迟要长得多。)S

图5.此图显示了首次将输入电源施加到LDO时的电路行为。TPS7B85-Q1PG引脚电压在首次上电时显示为红色,ENABLELATCH电压显示为蓝色。

PLD的实际输出如图6所示,包括上电序列期间大约15ms的延迟。

图6.这些是PLD的实际输出,包括上电序列期间大约15ms的延迟。EN_VBAT_PWR输出以红色显示,EN_LV_PWR的PLD输出以蓝色显示。

图7显示了DISABLE事件期间的PLD输出,描述了15ms的延迟。

图7.这将突出显示睡眠行为,显示EN_LV_PWR(蓝色)变为低电平,然后是EN_VBAT_PWR信号(红色)。

为什么PLD/LDO组合优于微控制器

这种基于硬件的低成本、低功耗解决方案用于处理电源启用和禁用功能,无需外部MCU,并且可以根据实际需求进行进一步定制。用户还可以选择订购预编程了逻辑设计的定制PLD。

预编程的PLD避免了为MCU编写和维护固件的时间和成本,同时也避免了在生产环境中对MCU进行编程。具有预编程PLD的这些省时功能以及TPLD801-Q1和TPS7B85-Q1硬件解决方案成本低的事实,能够有效节省整体系统费用。

TPLD801-Q1采用1.6×2.1mm的小封装,TPS7B85-Q1采用3×3mm封装,这有助于节省整个印刷电路板布局的空间。对于印刷电路板设计人员来说,这是非常有帮助的,因为他们经常面临着必须在同一电路板区域内安装更多功能的任务。

综上所述,使用LDO和PLD实现电源启用和禁用功能是一种高效、低成本且节省空间的解决方案,在电子系统设计中具有广阔的应用前景。

浙公网安备 33010502006866号

浙公网安备 33010502006866号