| 是否Rohs认证: | 不符合 | 生命周期: | Transferred |

| 零件包装代码: | QFP | 包装说明: | QFP, QFP68,1.1SQ,50 |

| 针数: | 68 | Reach Compliance Code: | unknown |

| 风险等级: | 5 | JESD-30 代码: | S-CQFP-G68 |

| JESD-609代码: | e0 | 长度: | 24.13 mm |

| 端子数量: | 68 | 最高工作温度: | 85 °C |

| 最低工作温度: | -40 °C | 封装主体材料: | CERAMIC, METAL-SEALED COFIRED |

| 封装代码: | QFP | 封装等效代码: | QFP68,1.1SQ,50 |

| 封装形状: | SQUARE | 封装形式: | FLATPACK |

| 电源: | 5 V | 认证状态: | Not Qualified |

| 座面最大高度: | 3.43 mm | 子类别: | Math Processors |

| 最大压摆率: | 136 mA | 最大供电电压: | 5.5 V |

| 最小供电电压: | 4.5 V | 标称供电电压: | 5 V |

| 表面贴装: | YES | 技术: | CMOS |

| 温度等级: | INDUSTRIAL | 端子面层: | Tin/Lead (Sn/Pb) |

| 端子形式: | GULL WING | 端子节距: | 1.27 mm |

| 端子位置: | QUAD | 宽度: | 24.13 mm |

| uPs/uCs/外围集成电路类型: | MATH PROCESSOR, COPROCESSOR | Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| TS68882VF20 | ATMEL |

获取价格 |

CMOS Enhanced Floating-point Co-processor |

|

| TS68882VF25 | ATMEL |

获取价格 |

CMOS Enhanced Floating-point Co-processor |

|

| TS68882VF33 | ATMEL |

获取价格 |

CMOS Enhanced Floating-point Co-processor |

|

| TS68882VR16 | ATMEL |

获取价格 |

CMOS Enhanced Floating-point Co-processor |

|

| TS68882VR20 | ATMEL |

获取价格 |

CMOS Enhanced Floating-point Co-processor |

|

| TS68882VR25 | ATMEL |

获取价格 |

CMOS Enhanced Floating-point Co-processor |

|

| TS68882VR33 | ATMEL |

获取价格 |

CMOS Enhanced Floating-point Co-processor |

|

| TS68930CC | STMICROELECTRONICS |

获取价格 |

IC,DSP,16-BIT,MOS,DIP,48PIN,CERAMIC |

|

| TS68930CP | ETC |

获取价格 |

Peripheral IC |

|

| TS68930CP/PXXX | ETC |

获取价格 |

16-Bit Digital Signal Processor |

|

英伟达驱动支持期限敲定:Maxwell/Pascal/Volta架构仅剩最后一年

英伟达驱动支持期限敲定:Maxwell/Pascal/Volta架构仅剩最后一年

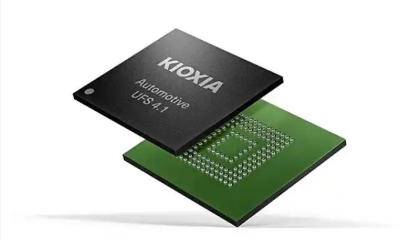

铠侠车用UFS 4.1闪存发布:性能飙升3.7倍,1TB容量改写车载存储格局

铠侠车用UFS 4.1闪存发布:性能飙升3.7倍,1TB容量改写车载存储格局

三星抢跑2纳米时代!Exynos 2600芯片或成Galaxy S26杀手锏

三星抢跑2纳米时代!Exynos 2600芯片或成Galaxy S26杀手锏

铠侠车规级UFS 4.1震撼发布:随机写入速度飙升至3.7倍

铠侠车规级UFS 4.1震撼发布:随机写入速度飙升至3.7倍