Si5347/46

DUAL/QUAD DSPLL ANY-FREQUENCY, ANY-OUTPUT

JITTER ATTENUATORS

Features

Four or two independent DSPLLs in a

single monolithic IC

Each DSPLL generates any output

frequency from any input frequency

Input frequency range:

Differential: 8 kHz to 750 MHz

LVCMOS: 8 kHz to 250 MHz

Output frequency range:

Automatic free-run and holdover modes

Fastlock feature for low nominal

bandwidths

Glitchless on-the-fly DSPLL frequency

changes

DCO mode: as low as 0.01 ppb steps

per DSPLL

Core voltage:

Differential: up to 712.5 MHz

LVCMOS: up to 250 MHz

Ultra low jitter:

<100 fs typ (12 kHz–20 MHz)

Flexible crosspoints route any input to

any output clock

Programmable jitter attenuation

bandwidth per DSPLL: 0.1 Hz to 4 kHz

programming range

Highly configurable outputs compatible

with LVDS, LVPECL, LVCMOS, CML,

and HCSL with programmable signal

amplitude

VDD: 1.8 V ±5%

9x9 mm

7x7 mm

VDDA: 3.3 V ±5%

Independent output clock supply pins:

3.3, 2.5, or 1.8 V

Output-output skew:

Ordering Information:

See section 8

<20 ps (typ) per DSPLL

Serial interface: I2C or SPI

In-circuit programmable with non-volatile

OTP memory

ClockBuilderTM Pro software tool

simplifies device configuration

Si5347: Quad DSPLL, 4 input,

4 or 8 output, 64 QFN

Si5346: Dual DSPLL, 4 input,

4 output, 44 QFN

Temperature range: –40 to +85 °C

Pb-free, RoHS-6 compliant

Functional Block Diagram

XTAL/

REFCLK

XA

XB

Si5347

Status monitoring (LOS, OOF, LOL)

Hitless input clock switching: automatic

or manual

OSC

÷INT

÷INT

÷INT

÷INT

Locks to gapped clock inputs

OUT0

OUT1

DSPLL

A

IN0

IN1

IN2

IN3

÷FRAC

÷FRAC

÷FRAC

÷FRAC

Device Selector Guide

OUT2

OUT3

OUT4

OUT5

OUT6

OUT7

DSPLL

B

Grade

PLLs/OUTs

Max Output Freq

712.5 MHz

712.5 MHz

712.5 MHz

350 MHz

Frequency Synthesis Modes

Integer + Fractional

Integer + Fractional

Integer + Fractional

Integer + Fractional

Integer + Fractional

Integer + Fractional

÷INT

÷INT

÷INT

÷INT

Si5347A

Si5347C

Si5346A

Si5347B

Si5347D

Si5346B

4/8

4/4

2/4

4/8

4/4

2/4

DSPLL

C

DSPLL

D

NVM

350 MHz

I2C/SPI

350 MHz

Control/

Status

Applications

OTN Muxponders and Transponders

10/40/100G network line cards

GbE/10 GbE/100 GbE Synchronous

Ethernet (ITU-T G.8262)

Carrier Ethernet switches

Broadcast video

XTAL/

REFCLK

XA

XB

Si5346

OSC

Description

÷INT

÷INT

÷INT

÷INT

IN0

OUT0

OUT1

÷FRAC

÷FRAC

÷FRAC

÷FRAC

The Si5347 is a high performance jitter attenuating clock multiplier which integrates four

any-frequency DSPLLs for applications that require maximum integration and independent

timing paths. The Si5346 is a dual DSPLL version in a smaller package. Each DSPLL has

access to any of the four inputs and can provide low jitter clocks on any of the device

outputs. Based on 4th generation DSPLL technology, these devices provide any-frequency

conversion with typical jitter performance under 100 fs. Each DSPLL supports independent

free-run, holdover modes of operation, as well as automatic and hitless input clock

DSPLL

A

IN1

IN2

IN3

OUT2

OUT3

DSPLL

B

NVM

I2C/SPI

switching. The Si5347/46 is programmable via

a serial interface with in-circuit

programmable non-volatile memory so that it always powers up in a known configuration.

Programming the Si5347/46 is easy with Silicon Labs’ ClockBuilder Pro software. Factory

pre-programmed devices are also available.

Control/

Status

Rev. 1.0 7/15

Copyright © 2015 by Silicon Laboratories

Si5347/46

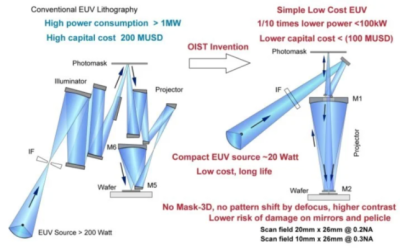

俄罗斯公布极紫外光刻机路线图 能否撼动ASML霸主地位?

俄罗斯公布极紫外光刻机路线图 能否撼动ASML霸主地位?

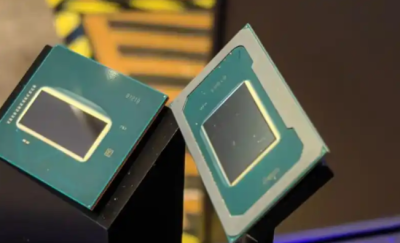

英特尔Panther Lake旗舰型号TDP升至45W,LPE核心首度开放调用权限

英特尔Panther Lake旗舰型号TDP升至45W,LPE核心首度开放调用权限

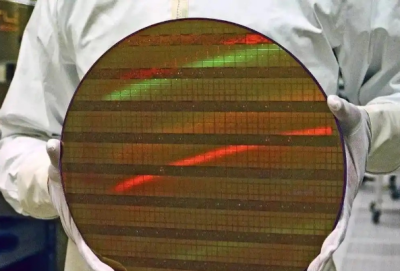

三星2nm晶圆代工降价三分之一 价格战能否撼动台积电霸主地位?

三星2nm晶圆代工降价三分之一 价格战能否撼动台积电霸主地位?

Vuzix联袂TCL华星光电 突破AR眼镜光学显示技术瓶颈

Vuzix联袂TCL华星光电 突破AR眼镜光学显示技术瓶颈