| 生命周期: | Obsolete | 零件包装代码: | WAFER |

| 包装说明: | DIE, WAFER | Reach Compliance Code: | unknown |

| 风险等级: | 5.77 | 地址总线宽度: | 2 |

| 总线兼容性: | 8049; 8051; 6800; 68000; Z80 | 外部数据总线宽度: | 8 |

| JESD-30 代码: | X-XUUC-N | 最高工作温度: | 85 °C |

| 最低工作温度: | -40 °C | 封装主体材料: | UNSPECIFIED |

| 封装代码: | DIE | 封装等效代码: | WAFER |

| 封装形状: | UNSPECIFIED | 封装形式: | UNCASED CHIP |

| 电源: | 2.5/3.3 V | 认证状态: | Not Qualified |

| 子类别: | Bus Controllers | 最大压摆率: | 6 mA |

| 最大供电电压: | 3.6 V | 最小供电电压: | 2.3 V |

| 标称供电电压: | 2.5 V | 表面贴装: | YES |

| 技术: | CMOS | 温度等级: | INDUSTRIAL |

| 端子形式: | NO LEAD | 端子位置: | UPPER |

| uPs/uCs/外围集成电路类型: | BUS CONTROLLER, I2C | Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| PCA9564_06 | NXP | Parallel bus to I2C-bus controller |

获取价格 |

|

| PCA9564BS | NXP | Parallel bus to I2C-bus controller |

获取价格 |

|

| PCA9564D | NXP | Parallel bus to I2C-bus controller |

获取价格 |

|

| PCA9564D,118 | NXP | PCA9564 - Parallel bus to I2C-bus controller SOP 20-Pin |

获取价格 |

|

| PCA9564N | NXP | Parallel bus to I2C-bus controller |

获取价格 |

|

| PCA9564N,112 | NXP | PCA9564 - Parallel bus to I2C-bus controller DIP 20-Pin |

获取价格 |

|

pcf8563芯片功能说明、参数分析、引脚说明

pcf8563芯片功能说明、参数分析、引脚说明

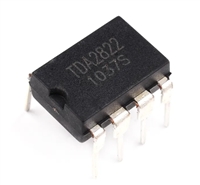

TDA2822资料手册:引脚说明、参数分析

TDA2822资料手册:引脚说明、参数分析

TJA1050资料数据分析、引脚说明、应用示例介绍

TJA1050资料数据分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍