| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| NB4N855SMR4 | ONSEMI |

获取价格 |

3.3 V, 1.5 Gb/s Dual AnyLevelTM to LVDS Receiver/Driver/Buffer/ Translator |

|

| NB4N855SMR4G | ONSEMI |

获取价格 |

3.3 V, 1.5 Gb/s Dual AnyLevelTM to LVDS Receiver/Driver/Buffer/ Translator |

|

| NB50E1-9.999MHZ | CALIBER |

获取价格 |

Parallel - Fundamental Quartz Crystal, 9.999MHz Nom, SMD, 4 PIN |

|

| NB50F1-3.500MHZ | CALIBER |

获取价格 |

Parallel - Fundamental Quartz Crystal, 3.5MHz Nom, SMD, 4 PIN |

|

| NB50F1-9.999MHZ | CALIBER |

获取价格 |

Parallel - Fundamental Quartz Crystal, 9.999MHz Nom, SMD, 4 PIN |

|

| NB50SM/24-C-D | COOPER |

获取价格 |

DC-DC Regulated Power Supply Module, 1 Output, 50W, Hybrid, PACKAGE-11 |

|

| NB50SM/28-B-D | COOPER |

获取价格 |

DC-DC Regulated Power Supply Module, 1 Output, 50W, Hybrid, PACKAGE-11 |

|

| NB50SM/28-B-I | COOPER |

获取价格 |

DC-DC Regulated Power Supply Module, 1 Output, 50W, Hybrid, PACKAGE-11 |

|

| NB50SM/2-B-D | COOPER |

获取价格 |

DC-DC Regulated Power Supply Module, 1 Output, 50W, Hybrid, PACKAGE-11 |

|

| NB50SM/5.2-A-D | COOPER |

获取价格 |

DC-DC Regulated Power Supply Module, 1 Output, 50W, Hybrid, PACKAGE-11 |

|

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

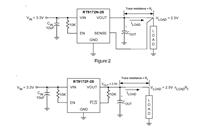

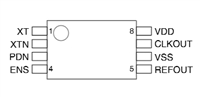

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明

一文带你了解SM8760CA资料:主要参数特征

一文带你了解SM8760CA资料:主要参数特征