| 是否Rohs认证: | 符合 | 生命周期: | Obsolete |

| 零件包装代码: | QLCC | 包装说明: | LEAD FREE, PLASTIC, LCC-28 |

| 针数: | 28 | Reach Compliance Code: | unknown |

| HTS代码: | 8542.39.00.01 | 风险等级: | 5.7 |

| 其他特性: | NECL MODE: VCC = 0V WITH VEE = -4.2V TO -5.7V | 系列: | 10E |

| JESD-30 代码: | S-PQCC-J28 | JESD-609代码: | e3 |

| 长度: | 11.505 mm | 逻辑集成电路类型: | D FLIP-FLOP |

| 湿度敏感等级: | 3 | 位数: | 9 |

| 功能数量: | 1 | 端子数量: | 28 |

| 最高工作温度: | 85 °C | 最低工作温度: | |

| 输出特性: | OPEN-EMITTER | 输出极性: | TRUE |

| 封装主体材料: | PLASTIC/EPOXY | 封装代码: | QCCJ |

| 封装形状: | SQUARE | 封装形式: | CHIP CARRIER |

| 峰值回流温度(摄氏度): | 260 | 传播延迟(tpd): | 1 ns |

| 认证状态: | Not Qualified | 座面最大高度: | 4.57 mm |

| 最大供电电压 (Vsup): | 5.7 V | 最小供电电压 (Vsup): | 4.2 V |

| 标称供电电压 (Vsup): | 5 V | 表面贴装: | YES |

| 技术: | ECL | 温度等级: | OTHER |

| 端子面层: | Tin (Sn) | 端子形式: | J BEND |

| 端子节距: | 1.27 mm | 端子位置: | QUAD |

| 处于峰值回流温度下的最长时间: | 40 | 触发器类型: | POSITIVE EDGE |

| 宽度: | 11.505 mm | 最小 fmax: | 700 MHz |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| MC10E143FNG | ONSEMI |

获取价格 |

5V ECL 9-Bit Hold Register |

|

| MC10E143FNR2 | ONSEMI |

获取价格 |

5V ECL 9-Bit Hold Register |

|

| MC10E143FNR2G | ONSEMI |

获取价格 |

5V ECL 9-Bit Hold Register |

|

| MC10E150 | ONSEMI |

获取价格 |

6-BIT D LATCH |

|

| MC10E150_06 | ONSEMI |

获取价格 |

5V ECL 6-Bit D Latch |

|

| MC10E150FN | ONSEMI |

获取价格 |

5V ECL 6-Bit D Latch |

|

| MC10E150FN | MOTOROLA |

获取价格 |

6-BIT D LATCH |

|

| MC10E150FNG | ONSEMI |

获取价格 |

5V ECL 6-Bit D Latch |

|

| MC10E150FNR2 | ONSEMI |

获取价格 |

5V ECL 6-Bit D Latch |

|

| MC10E150FNR2G | ONSEMI |

获取价格 |

5V ECL 6-Bit D Latch |

|

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

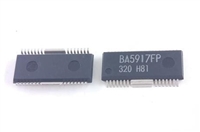

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐