| 是否无铅: | 含铅 | 是否Rohs认证: | 符合 |

| 生命周期: | Active | 包装说明: | HVQCCN, |

| 针数: | 40 | Reach Compliance Code: | compliant |

| 风险等级: | 5.62 | JESD-30 代码: | S-XQCC-N40 |

| JESD-609代码: | e3 | 长度: | 6 mm |

| 湿度敏感等级: | 1 | 功能数量: | 1 |

| 端子数量: | 40 | 最高工作温度: | 85 °C |

| 最低工作温度: | -40 °C | 封装主体材料: | UNSPECIFIED |

| 封装代码: | HVQCCN | 封装形状: | SQUARE |

| 封装形式: | CHIP CARRIER, HEAT SINK/SLUG, VERY THIN PROFILE | 峰值回流温度(摄氏度): | 260 |

| 座面最大高度: | 0.9 mm | 标称供电电压: | 3.3 V |

| 表面贴装: | YES | 电信集成电路类型: | RF AND BASEBAND CIRCUIT |

| 温度等级: | INDUSTRIAL | 端子面层: | Tin (Sn) |

| 端子形式: | NO LEAD | 端子节距: | 0.5 mm |

| 端子位置: | QUAD | 处于峰值回流温度下的最长时间: | 30 |

| 宽度: | 6 mm | Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| HMC832LP6GE | ADI | 暂无描述 |

获取价格 |

|

| HMC832LP6GE | HITTITE | Fractional-N PLL with Integrated VCO 25 MHz to 3000 MHz |

获取价格 |

|

| HMC832LP6GETR | ADI | Wideband PLL+VCO (3.3V), 25 - 3000 MHz |

获取价格 |

|

| HMC832LP6GETR | HITTITE | PLL/Frequency Synthesis Circuit, |

获取价格 |

|

| HMC833LP6GE | HITTITE | Built in Digital Self Test |

获取价格 |

|

| HMC833LP6GE | ADI | Fractional-N PLL with Integrated VCO, 25 - 6000 MHz |

获取价格 |

|

MC34063开关稳压器:全面参数解析与设计指南

MC34063开关稳压器:全面参数解析与设计指南

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

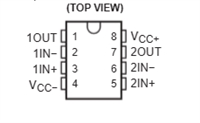

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析