| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| CY7C457-30JIR | CYPRESS |

获取价格 |

FIFO, 2KX18, Synchronous, CMOS, PQCC52, PLASTIC, LCC-52 |

|

| CY7C457-30JIT | CYPRESS |

获取价格 |

FIFO, 2KX18, 20ns, Synchronous, CMOS, PQCC52, PLASTIC, LCC-52 |

|

| CY7C457-30LMB | CYPRESS |

获取价格 |

FIFO, 2KX18, 30ns, Synchronous, CMOS, CQCC52, CERAMIC, LCC-52 |

|

| CY7C457-30NI | ETC |

获取价格 |

x18 Synchronous FIFO |

|

| CY7C460-15DC | ETC |

获取价格 |

x9 Asynchronous FIFO |

|

| CY7C460-15DMB | CYPRESS |

获取价格 |

FIFO, 8KX9, 15ns, Asynchronous, CMOS, CDIP28, 0.600 INCH, CERDIP-28 |

|

| CY7C460-15JC | CYPRESS |

获取价格 |

FIFO, 8KX9, 15ns, Asynchronous, CMOS, PQCC32, PLASTIC, LCC-32 |

|

| CY7C460-15JCR | CYPRESS |

获取价格 |

FIFO, 8KX9, 15ns, Asynchronous, CMOS, PQCC32, PLASTIC, LCC-32 |

|

| CY7C460-15JI | ROCHESTER |

获取价格 |

8K X 9 OTHER FIFO, 15 ns, PQCC32, PLASTIC, LCC-32 |

|

| CY7C460-15JIT | CYPRESS |

获取价格 |

FIFO, 8KX9, 15ns, Asynchronous, CMOS, PQCC32, PLASTIC, LCC-32 |

|

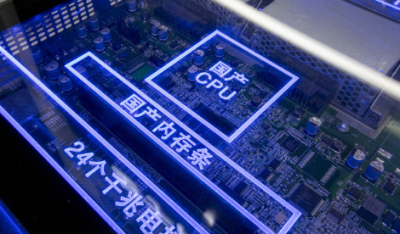

国产AI算力崛起!阿里百度用自研芯片开启AI新时代

国产AI算力崛起!阿里百度用自研芯片开启AI新时代

中国三大运营商全面布局eSIM业务 用户何时能用上?

中国三大运营商全面布局eSIM业务 用户何时能用上?

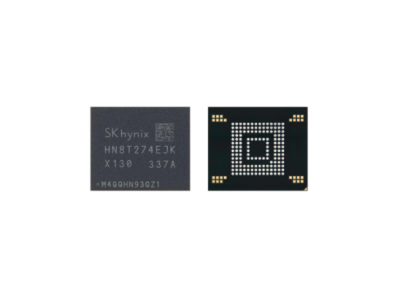

ZUFS 4.1问世!SK海力士新一代闪存如何改写移动端性能格局?

ZUFS 4.1问世!SK海力士新一代闪存如何改写移动端性能格局?

博通斩获OpenAI百亿订单,能否撼动英伟达AI芯片霸主地位

博通斩获OpenAI百亿订单,能否撼动英伟达AI芯片霸主地位