AI芯片封装革命将至?台积电FOPLP技术路线图曝光

当全球AI算力竞赛进入白热化阶段,台积电正在下一盘关于芯片封装的战略大棋。据台媒最新披露,这家半导体巨头计划在嘉义AP7厂区建设CoPoS先进封装量产基地,目标2028至2029年实现商业化生产。这项融合FOPLP与CoWoS优势的颠覆性技术,或将重新定义AI芯片的制造规则方形面板替代圆形晶圆的效率革命

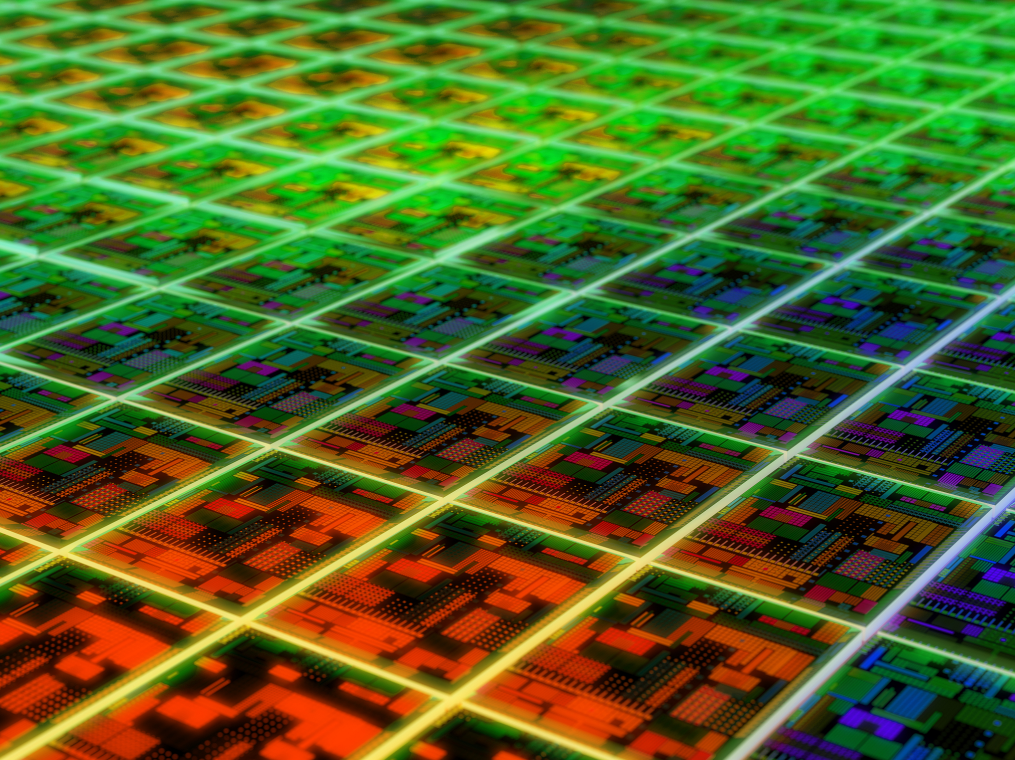

CoPoS全称Chip on Panel on Substrate,其核心创新在于用方形面板取代传统晶圆作为载体。相较于12英寸圆形晶圆不可避免的边角材料浪费,方形基板的利用率可提升20%以上。更关键的是,这种设计突破300mm晶圆的物理限制,允许扩展至更大尺寸基板——这对需要集成上千亿晶体管的下一代AI芯片至关重要。

台积电已规划分三步走的技术路线:2026年下半年在采钰厂区建成试验线并试产;2027年进入技术开发攻坚阶段;2028年完成制程验证。这种稳扎稳打的节奏,显示出企业对这项跨代技术的审慎态度。

英伟达AMD博通组队“尝鲜”

市场消息显示,台积电当前最大CoWoS客户英伟达将成为CoPoS的首批采用者。AMD与博通也表现出强烈兴趣,这三家占据全球AI芯片90%市场份额的巨头,其集体转向将极大加速新技术产业化进程。值得注意的是,博通与台积电合作开发的CPO(共封装光学)技术已成功整合3nm制程,未来可能与CoPoS形成协同效应,突破传统铜线路的传输瓶颈。

嘉义厂区承载台积电封装野心

选择嘉义AP7作为量产基地颇具深意。该园区毗邻台南科学园区,能实现与5nm/3nm晶圆厂的供应链协同。台积电近年来在先进封装领域投资超200亿美元,CoPoS量产后,其封装产能将形成CoWoS、InFO、SoIC、CoPoS四足鼎立的格局。行业分析师指出,这标志着半导体产业从“制程竞赛”正式进入“封装战争”新纪元。

随着AI芯片向万亿晶体管规模迈进,传统封装技术已接近物理极限。台积电此次技术押注,不仅关乎企业自身的技术护城河,更可能决定未来五年全球算力基础设施的竞争格局。当2029年量产钟声敲响时,半导体产业或将迎来新一轮洗牌。

491

491

浙公网安备 33010502006866号

浙公网安备 33010502006866号