当AI巨浪席卷全球,每秒9600兆次的数据传输能带来怎样的算力革命?这个问题在瑞萨电子最新发布的第六代RCD芯片上得到了惊艳解答。这家半导体巨头昨日扔出一枚技术深水炸弹——全球首款支持DDR5-9600 RDIMM的寄存时钟驱动器横空出世,以10%的带宽提升刷新了内存接口技术的性能天花板。

带宽跃迁背后的技术密码 这款代号RRG5006x的芯片堪称内存世界的"交响乐指挥家",其9600MT/s的数据传输速率相较当前8800MT/s标准实现了质的飞跃。这不仅仅是数字游戏,其搭载的八Tap均衡器架构配合1.5mV精度的电压调节系统,如同给数据流装上了纳米级调音台。实测显示,该技术可将信号畸变降低至前代产品的三分之一,为AI训练时海量参数的并行传输铺平道路。

在硅基魔法背后,隐藏着更精妙的系统设计。增强型DESTM诊断引擎就像给内存通道装上了CT扫描仪,能实时捕捉信号质量波形图。当HPC集群处理万亿级矩阵运算时,这套系统可在纳秒级完成信号裕量可视化诊断,将传统的事后分析升级为预防性维护。某合作厂商测试数据显示,该功能使内存子系统宕机概率下降40%。

为AI时代量身定制的性能引擎 面对大模型参数爆炸式增长,瑞萨工程师在芯片内部构建了独特的负载自适应架构。通过动态时序控制算法,当128个DIMM组成的内存池同时工作时,信号衰减可控制在3dB以内。这意味着单台服务器就能支持千亿参数模型的实时推理,而不必担心"内存墙"效应。大型科技公司的实验室数据显示,该技术可使LLM训练迭代周期缩短15%。

能效优化同样令人瞩目。新架构在8800MT/s速率下功耗反而比前代降低8%,这种反常的"性能越高越省电"特性,源自其创新的时钟门控技术。当检测到内存访问间歇期,芯片会智能关闭未使用通道的时钟树,就像城市路灯系统般按需供电。这对于年耗电量以兆瓦计的数据中心而言,意味着可观的电费节约。

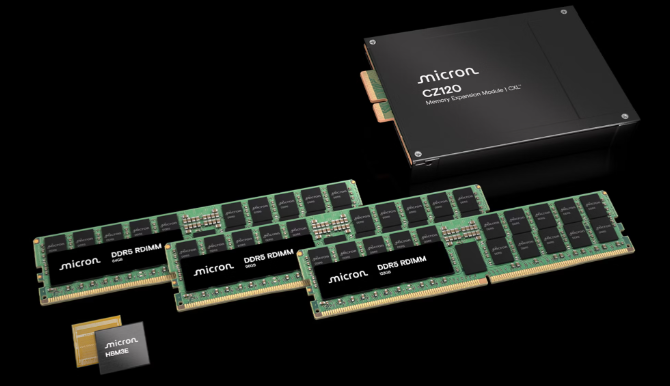

产业链协同的创新范式 瑞萨此次没有选择闭门造车,而是构建了包含CPU厂商、DRAM供应商和终端用户的"黄金三角"合作生态。这种协同创新模式确保RCD芯片与各大厂商的DDR5颗粒完美适配,就像为不同乐器定制专属乐谱。业内人士透露,采用该方案的OEM厂商已实现单内存通道94%的理论带宽利用率。

量产时间表显示,这颗芯片将于2027年上半年规模上市,正好赶上全球AI基础设施的升级浪潮。正如瑞萨内存接口事业部副总裁所言,这不仅是技术参数的突破,更是对算力民主化的重要推动。当9600MT/s的内存带宽成为标配,或许我们距离真正的通用人工智能又会近一步。

浙公网安备 33010502006866号

浙公网安备 33010502006866号