ACS8526 LC/P LITE

ADVANCED COMMUNICATIONS

Introduction

The ACS8526 is a highly integrated, single-chip solution

for protection switching of two SEC inputs from, for

example, Master and Slave SETS clock cards sources, for

Line Cards in a SONET or SDH Network Element. The

ACS8526 has fast activity monitors on the SEC clock

inputs.

FINAL

DATASHEET

APLL bandwidth is set four orders of magnitude higher

than the DPLL bandwidth. This ensures that the overall

system performance still maintains the advantage of

consistent behavior provided by the digital approach. The

DPLLs are clocked by the external oscillator module (TCXO

or XO) so that prior to initial lock (with no input reference)

or in Digital Holdover, the frequency stability is only

determined by the stability of the external oscillator

module. This gives the key advantage of confining all

temperature critical components to one well defined and

pre-calibrated oscillator module, whose performance can

be chosen to match the application. All performance

parameters of the DPLLs are programmable without the

need to understand detailed PLL equations. Bandwidth,

damping factor and lock range can all be configured

under software control.

The ACS8526 can be used as a standalone part without

the serial interface where all input and output frequencies

are set by external control using the IP_FREQ and

OP_FREQ pins. These pins determine the default

power-up or reset state of internal registers, that in turn

determine the I/O frequencies.

If more detailed control is required, then the registers

within the device can be re-configured, after an

initialization period, by writes through the serial interface.

The SRCSW pin is used to select one of the two SEC inputs

to lock to. The SRCSW pin must remain High for at least

251 ms following power-up or reset (251 ms after the

PORB signal has gone High). SRCSW Low following a

power-up or reset is not supported.

The hardware set-up configures a subset of the registers

in the register block, with the remainder adopting their

default settings. If hardware set-up alone is insufficient

for configuring, controlling and monitoring the device for a

particular application, then access to the full set of

registers for these purposes is provided by an SPI

compatible serial interface port.

The ACS8526 has two SEC inputs from which it can

generate independent clocks on outputs 01 and 02 with

a total of 53 possible output frequencies. In addition,

there are two Sync outputs; 8 kHz Frame Synchronization

(FrSync) signal and a 2 kHz Multi-Frame Synchronization

(MFrSync) signal.

Each register (8-bit wide data field) is identified by and

referred to by its hexadecimal address and name, e.g.

Reg. 7D cnfg_LOS_alarm. The “Register Map” on page 30

summarizes the content of all of the registers, and each

register is individually described in the subsequent

Register Tables, organized in order of ascending Address

(hexadecimal), in the “Register Descriptions” from

page 32 onwards.

Initially the ACS8526 generates a stable, low-noise clock

signal at a frequency to the same accuracy as the external

oscillator, or it can be made more accurate via software

calibration to within ±0.02 ppm. The device always

attempts to lock to one of its inputs (according to the

value on the SRCSW pin). Once locked to a reference the

accuracy of the output clock is determined directly by the

accuracy of the input reference. In the absence of any

input references the device simply maintains its most

recent frequency in a Digital Holdover mode. However, as

soon as the DPLL detects an input presence, it will

attempt to lock to it and will not “qualify” it first. As soon

as the DPLL detects a failure on the input, the DPLL

freezes its operating frequency and raises the LOS alarm

on device pin LOS_ALARM.

An Evaluation board and intuitive GUI-based software

package is available for device introduction. This has its

own documentation “ACS8526-EVB”.

General Description

The following description refers to the Block Diagram

(Figure 1 on page 1).

Inputs

The overall PLL loop bandwidth, damping, pull-in range

and frequency accuracy are all determined by digital

parameters that provide a consistent level of

The ACS8526 SETS device has two TTL/CMOS compatible

SEC input ports. They are 3 V and 5 V compatible (with

clamping if required by connecting the VDD5V pin). Refer

performance. An Analog PLL (APLL) takes the signal from to the “Electrical Specifications” on page 61 for more

the DPLL output and provides a lower jitter output. The

information on electrical compatibility.

Revision 4.01/June 2006 © Semtech Corp.

Page6

www.semtech.com

MC34063开关稳压器:全面参数解析与设计指南

MC34063开关稳压器:全面参数解析与设计指南

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

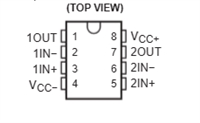

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析