A29L004A Series

Requirements for Reading Array Data

The device enters the CMOS standby mode when the

&

CE

pins (

only on 32-pin PLCC & (s)TSOP

CE

packages) are both held at VCC ± 0.3V. (Note that this is a

more restricted voltage range than VIH.) If and

RESET

To read array data from the outputs, the system must drive the

and

pins to VIL.

is the power control and selects

CE

OE

OE

the output pins.

CE

is the output control and gates array data to

should remain at VIH all the time during

CE

RESET

the device.

(N/A on 32-pin PLCC & (s)TSOP packages) are held at VIH,

but not within VCC ± 0.3V, the device will be in the standby

mode, but the standby current will be greater. The device

requires the standard access time (tCE) before it is ready to

read data.

If the device is deselected during erasure or programming, the

device draws active current until the operation is completed.

ICC3 and ICC4 in the DC Characteristics tables represent the

standby current specification.

WE

read operation. The internal state machine is set for reading

array data upon device power-up, or after a hardware reset.

This ensures that no spurious alteration of the memory content

occurs during the power transition. No command is necessary

in this mode to obtain array data. Standard microprocessor

read cycles that assert valid addresses on the device address

inputs produce valid data on the device data outputs. The

device remains enabled for read access until the command

register contents are altered.

Automatic Sleep Mode

See "Reading Array Data" for more information. Refer to the

AC Read Operations table for timing specifications and to the

Read Operations Timings diagram for the timing waveforms,

lCC1 in the DC Characteristics table represents the active

current specification for reading array data.

The automatic sleep mode minimizes Flash device energy

consumption. The device automatically enables this mode

when addresses remain stable for tACC +30ns. The automatic

sleep mode is independent of the

,

and

control

OE

WE

CE

signals. Standard address access timings provide new data

when addresses are changed. While in sleep mode, output

data is latched and always available to the system. ICC4 in the

DC Characteristics table represents the automatic sleep mode

current specification.

Writing Commands/Command Sequences

To write a command or command sequence (which includes

programming data to the device and erasing sectors of

memory), the system must drive

and

to VIL, and

CE

WE

Output Disable Mode

to VIH. The device features an Unlock Bypass mode to

OE

facilitate faster programming. Once the device enters the

Unlock Bypass mode, only two write cycles are required to

program a byte, instead of four.

The “Byte Program Command Sequence” section has details

on programming data to the device using both standard and

Unlock Bypass command sequence. An erase operation can

erase one sector, multiple sectors, or the entire device. The

Sector Address Tables indicate the address range that each

sector occupies. A "sector address" consists of the address

inputs required to uniquely

When the

input is at VIH, output from the device is

OE

disabled. The output pins are placed in the high impedance

state.

: Hardware Reset Pin (N/A on 32-pin PLCC &

RESET

(s)TSOP packages)

The pin provides a hardware method of resetting the

RESET

device to reading array data. When the system drives the

pin low for at least a period of tRP, the device

RESET

select a sector. See the "Command Definitions" section for

immediately terminates any operation in progress, tristates all

data output pins, and ignores all read/write attempts for the

duration of the

details on erasing

a

sector or the entire chip, or

suspending/resuming the erase operation.

pulse. The device also resets the

RESET

After the system writes the autoselect command sequence,

the device enters the autoselect mode. The system can then

read autoselect codes from the internal register (which is

separate from the memory array) on I/O7 - I/O0. Standard read

cycle timings apply in this mode. Refer to the "Autoselect

Mode" and "Autoselect Command Sequence" sections for

more information.

ICC2 in the DC Characteristics table represents the active

current specification for the write mode. The "AC

Characteristics" section contains timing specification tables

and timing diagrams for write operations.

internal state machine to reading array data. The operation

that was interrupted should be reinitiated once the device is

ready to accept another command sequence, to ensure data

integrity.

Current is reduced for the duration of the

pulse.

RESET

When

is held at VSS ± 0.3V, the device draws CMOS

RESET

standby current (ICC4 ). If

is held at VIL but not within

RESET

VSS ± 0.3V, the standby current will be greater.

The pin may be tied to the system reset circuitry. A

RESET

system reset would thus also reset the Flash memory,

enabling the system to read the boot-up firmware from the

Flash memory.

Program and Erase Operation Status

If

is asserted during a program or erase operation,

RESET

the RY/

During an erase or program operation, the system may check

the status of the operation by reading the status bits on I/O7 -

I/O0. Standard read cycle timings and ICC read specifications

apply. Refer to "Write Operation Status" for more information,

and to each AC Characteristics section for timing diagrams.

pin remains a “0” (busy) until the internal reset

BY

operation is complete, which requires a time tREADY (during

Embedded Algorithms). The system can thus monitor RY/

BY

to determine whether the reset operation is complete. If

is asserted when a program or erase operation is not

Standby Mode

RESET

executing (RY/

pin is “1”), the reset operation is completed

BY

within a time of tREADY (not during Embedded Algorithms). The

system can read data tRH after the pin return to VIH.

When the system is not reading or writing to the device, it can

place the device in the standby mode. In this mode, current

consumption is greatly reduced, and the outputs are placed in

RESET

Refer to the AC Characteristics tables for

and diagram.

parameters

RESET

the high impedance state, independent of the

input.

OE

PRELIMINARY (March, 2005, Version 0.0)

5

AMIC Technology, Corp.

MC34063开关稳压器:全面参数解析与设计指南

MC34063开关稳压器:全面参数解析与设计指南

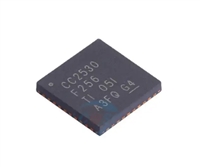

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

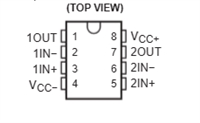

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析