AD2S80A

CONVERTER OPERATION

POSITION OUTPUT

When connected in a circuit such as shown in Figure 1 the

AD2S80A operates as a tracking resolver-to-digital converter

and forms a Type 2 closed-loop system. The output will auto-

matically follow the input for speeds up to the selected maximum

tracking rate. No convert command is necessary as the conversion

is automatically initiated by each LSB increment, or decre-

ment, of the input. Each LSB change of the converter initiates a

BUSY pulse.

The resolver shaft position is represented at the converter output

by a natural binary parallel digital word. As the digital position

output of the converter passes through the major carries, i.e., all

“1s” to all “0s” or the converse, a RIPPLE CLOCK (RC) logic

output is initiated indicating that a revolution or a pitch of the

input has been completed.

The direction of input rotation is indicated by the DIRECTION

(DIR) logic output. This direction data is always valid in advance

of a RIPPLE CLOCK pulse and, as it is internally latched, only

changing state (1 LSB min change) with a corresponding

change in direction.

The AD2S80A is remarkably tolerant of input amplitude and

frequency variation because the conversion depends only on the

ratio of the input signals. Consequently there is no need for

accurate, stable oscillator to produce the reference signal. The

inclusion of the phase sensitive detector in the conversion loop

ensures a high immunity to signals that are not coherent or are

in quadrature with the reference signal.

Both the RIPPLE CLOCK pulse and the DIRECTION data

are unaffected by the application of the INHIBIT. The static

positional accuracy quoted is the worst case error that can occur

over the full operating temperature excluding the effects of

offset signals at the INTEGRATOR INPUT (which can be

trimmed out—see Figure 1), and with the following conditions:

input signal amplitudes are within 10% of the nominal; phase

shift between signal and reference is less than 10 degrees.

SIGNAL CONDITIONING

The amplitude of the SINE and COSINE signal inputs should

be maintained within 10% of the nominal values if full perfor-

mance is required from the velocity signal.

These operating conditions are selected primarily to establish a

repeatable acceptance test procedure which can be traced to

national standards. In practice, the AD2S80A can be used well

outside these operating conditions providing the above points

are observed.

The digital position output is relatively insensitive to amplitude

variation. Increasing the input signal levels by more than 10%

will result in a loss in accuracy due to internal overload. Reduc-

ing levels will result in a steady decline in accuracy. With the

signal levels at 50% of the correct value, the angular error will

increase to an amount equivalent to 1.3 LSB. At this level the

repeatability will also degrade to 2 LSB and the dynamic response

will also change, since the dynamic characteristics are propor-

tional to the signal level.

VELOCITY SIGNAL

The tracking converter technique generates an internal signal at

the output of the integrator (the INTEGRATOR OUTPUT

pin) that is proportional to the rate of change of the input angle.

This is a dc analog output referred to as the VELOCITY signal.

The AD2S80A will not be damaged if the signal inputs are applied

to the converter without the power supplies and/or the reference.

In many applications it is possible to use the velocity signal of

the AD2S80A to replace a conventional tachogenerator.

REFERENCE INPUT

The amplitude of the reference signal applied to the converter’s

input is not critical, but care should be taken to ensure it is kept

within the recommended operating limits.

DC ERROR SIGNAL

The signal at the output of the phase sensitive detector

(DEMODULATOR OUTPUT) is the signal to be nulled by

the tracking loop and is, therefore, proportional to the error

between the input angle and the output digital angle. This is the

dc error of the converter; and as the converter is a Type 2 servo

loop, it will increase if the output fails to track the input for any

reason. It is an indication that the input has exceeded the maxi-

mum tracking rate of the converter or, due to some internal

malfunction, the converter is unable to reach a null. By connect-

ing two external comparators, this voltage can be used as a

“built-in-test.”

The AD2S80A will not be damaged if the reference is sup-

plied to the converter without the power supplies and/or the

signal inputs.

HARMONIC DISTORTION

The amount of harmonic distortion allowable on the signal and

reference lines is 10%.

Square waveforms can be used but the input levels should be

adjusted so that the average value is 1.9 V rms. (For example, a

square wave should be 1.9 V peak.) Triangular and sawtooth

waveforms should have a amplitude of 2 V rms.

Note: The figure specified of 10% harmonic distortion is for

calibration convenience only.

REV. B

–7–

MAX3232 RS-232电平转换器资料手册参数分析

MAX3232 RS-232电平转换器资料手册参数分析

MAX485 RS-485/RS-422收发器资料手册参数分析

MAX485 RS-485/RS-422收发器资料手册参数分析

74HC245八路双向总线收发器:资料手册参数分析

74HC245八路双向总线收发器:资料手册参数分析

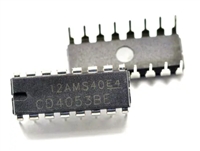

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4053模拟多路复用器/解复用器:资料手册参数分析