0

Virtex-5 FPGA Data Sheet:

DC and Switching Characteristics

0

0

DS202 (v5.5) June 17, 2016

Product Specification

Virtex-5 FPGA Electrical Characteristics

Virtex®-5 FPGAs are available in -3, -2, -1 speed grades,

with -3 having the highest performance. Virtex-5 FPGA DC

and AC characteristics are specified for both commercial

and industrial grades. Except the operating temperature

range or unless otherwise noted, all the DC and AC

electrical parameters are the same for a particular speed

grade (that is, the timing characteristics of a -1 speed grade

industrial device are the same as for a -1 speed grade

commercial device). However, only selected speed grades

and/or devices might be available in the industrial range.

•

•

•

•

•

•

Virtex-5 Family Overview

Virtex-5 FPGA User Guide

Virtex-5 FPGA Configuration Guide

Virtex-5 FPGA XtremeDSP™ Design Considerations

Virtex-5 FPGA Packaging and Pinout Specification

Embedded Processor Block in Virtex-5 FPGAs Reference

Guide

Virtex-5 FPGA RocketIO™ GTP Transceiver User Guide

Virtex-5 FPGA RocketIO GTX Transceiver User Guide

Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC User

Guide

Virtex-5 FPGA Integrated Endpoint Block User Guide for

PCI Express® Designs

Virtex-5 FPGA System Monitor User Guide

Virtex-5 FPGA PCB Designer’s Guide

•

•

•

All supply voltage and junction temperature specifications

are representative of worst-case conditions. The

parameters included are common to popular designs and

typical applications.

•

•

•

This Virtex-5 FPGA data sheet, part of an overall set of

documentation on the Virtex-5 family of FPGAs, is available

on the Xilinx website:

All specifications are subject to change without notice.

Virtex-5 FPGA DC Characteristics

Table 1: Absolute Maximum Ratings

Symbol

VCCINT

VCCAUX

VCCO

VBATT

VREF

Description

Units

Internal supply voltage relative to GND

–0.5 to 1.1

–0.5 to 3.0

–0.5 to 3.75

–0.5 to 4.05

–0.5 to 3.75

–0.75 to 4.05

V

V

V

V

V

V

Auxiliary supply voltage relative to GND

Output drivers supply voltage relative to GND

Key memory battery backup supply

Input reference voltage

3.3V I/O input voltage relative to GND(4) (user and dedicated I/Os)

–0.95 to 4.4

(Commercial Temperature)

–0.85 to 4.3

(Industrial Temperature)

3.3V I/O input voltage relative to GND (restricted to maximum of 100 user I/Os)(5)

V

(3)

VIN

2.5V or below I/O input voltage relative to GND (user and dedicated I/Os)

Current applied to an I/O pin, powered or unpowered

Total current applied to all I/O pins, powered or unpowered

Voltage applied to 3-state 3.3V output(4) (user and dedicated I/Os)

Voltage applied to 3-state 2.5V or below output (user and dedicated I/Os)

Storage temperature (ambient)

–0.75 to VCCO + 0.5

100

V

mA

mA

V

V

°C

°C

IIN

100

–0.75 to 4.05

–0.75 to VCCO + 0.5

–65 to 150

+220

VTS

TSTG

TSOL

TJ

Maximum soldering temperature(2)

Maximum junction temperature(2)

+125

°C

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings might cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute

Maximum Ratings conditions for extended periods of time might affect device reliability.

2. For soldering guidelines, refer to UG112: Device Package User Guide. For thermal considerations, refer to UG195: Virtex-5 FPGA Packaging and

Pinout Specification on the Xilinx website.

3. 3.3V I/O absolute maximum limit applied to DC and AC signals.

4. For 3.3V I/O operation, refer to UG190: Virtex-5 FPGA User Guide, Chapter 6, 3.3V I/O Design Guidelines.

5. For more flexibility in specific designs, a maximum of 100 user I/Os can be stressed beyond the normal specification for no more than 20% of a data period

.

© 2006–2010, 2014, 2016 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx

in the United States and other countries. PowerPC is a trademark of IBM Corp. and is used under license. PCI, PCI Express, PCIe, and PCI-X are trademarks of PCI-SIG. All

other trademarks are the property of their respective owners.

DS202 (v5.5) June 17, 2016

www.xilinx.com

Product Specification

1

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

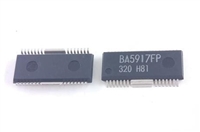

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐