| 是否Rohs认证: | 符合 | 生命周期: | Active |

| 包装说明: | BGA, BGA829,29X29,50 | Reach Compliance Code: | compliant |

| 风险等级: | 5.65 | JESD-30 代码: | S-PBGA-B829 |

| 端子数量: | 829 | 封装主体材料: | PLASTIC/EPOXY |

| 封装代码: | BGA | 封装等效代码: | BGA829,29X29,50 |

| 封装形状: | SQUARE | 封装形式: | GRID ARRAY |

| 电源: | 1.35,1.5,1.8/2.5,3.3 V | 认证状态: | Not Qualified |

| 子类别: | Other Microprocessor ICs | 表面贴装: | YES |

| 端子形式: | BALL | 端子节距: | 1.27 mm |

| 端子位置: | BOTTOM | Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| QG82910GML/SL8G8 | INTEL |

获取价格 |

Memory Controller, PBGA1257 |

|

| QG82910GMLE/SLA9L | INTEL |

获取价格 |

Memory Controller, CMOS, PBGA1257 |

|

| QG82915GME/SLA9K | INTEL |

获取价格 |

Memory Controller, CMOS, PBGA1257 |

|

| QG82915GMS/SL8G9 | INTEL |

获取价格 |

Memory Controller |

|

| QG82915PM/SL8G7 | INTEL |

获取价格 |

Memory Controller, PBGA1257 |

|

| QG82945G | INTEL |

获取价格 |

Intel® 945G Express and Intel® 945GC Expres |

|

| QG82945GC | INTEL |

获取价格 |

Intel® 945G Express and Intel® 945GC Expres |

|

| QG82945GCSLA9C | INTEL |

获取价格 |

DRAM Controller, 64M X 16, CMOS, PBGA1202, 34 X 34 MM, 0.80 MM PITCH, FCBGA-1202 |

|

| QG82945GM | INTEL |

获取价格 |

Mobile Intel 945GM Express Chipset for Embedded Computing |

|

| QG82945GMS | INTEL |

获取价格 |

Memory Controller, CMOS, PBGA998 |

|

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

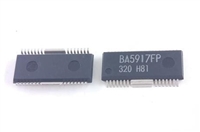

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐