| 品牌 | Logo | 应用领域 |

| 三菱 - MITSUBISHI | 动态存储器 | |

| 页数 | 文件大小 | 规格书 |

| 39页 | 341K |  |

| 描述 | ||

| 2,415,919,104-BIT (33,554,432-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module | ||

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| MH32D72KLH-75 | MITSUBISHI |

获取价格 |

2,415,919,104-BIT (33,554,432-WORD BY 72-BIT) Double Data Rate Synchronous DRAM Module |

|

| MH32D72KTH-10 | MITSUBISHI |

获取价格 |

DDR DRAM Module, 32MX72, 0.8ns, CMOS, DIMM-184 |

|

| MH32D72KTH-75 | MITSUBISHI |

获取价格 |

DDR DRAM Module, 32MX72, 0.75ns, CMOS, DIMM-184 |

|

| MH32FAD | MTRONPTI |

获取价格 |

8 pin DIP, 3.3 or 5.0 Volt, HCMOS/TTL Clock Oscillator |

|

| MH32FAD0.6250MHZ | MTRONPTI |

获取价格 |

Oscillator |

|

| MH32FAD01.0000MHZ | MTRONPTI |

获取价格 |

HCMOS/TTL Output Clock Oscillator, 1MHz Min, 80MHz Max, 1MHz Nom, |

|

| MH32FAD-1.0000MHZ | MTRONPTI |

获取价格 |

Oscillator |

|

| MH32FAD67.0000MHZ | MTRONPTI |

获取价格 |

Oscillator, |

|

| MH32FADFREQ1 | MTRONPTI |

获取价格 |

CMOS/TTL Output Clock Oscillator, 0.625MHz Min, 50MHz Max, HALF SIZE, NICKEL HEADER, DIP-4 |

|

| MH32FADFREQ2 | MTRONPTI |

获取价格 |

CMOS/TTL Output Clock Oscillator, 50.001MHz Min, 60MHz Max, HALF SIZE, NICKEL HEADER, DIP- |

|

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

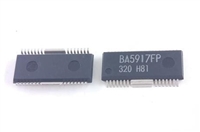

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐