| 是否无铅: | 不含铅 | 生命周期: | Not Recommended |

| 包装说明: | SSOP, | Reach Compliance Code: | compliant |

| Factory Lead Time: | 9 weeks | 风险等级: | 5.7 |

| JESD-30 代码: | R-PDSO-G28 | 长度: | 10.2 mm |

| I/O 线路数量: | 16 | 端口数量: | 2 |

| 端子数量: | 28 | 最高工作温度: | 85 °C |

| 最低工作温度: | -40 °C | 封装主体材料: | PLASTIC/EPOXY |

| 封装代码: | SSOP | 封装形状: | RECTANGULAR |

| 封装形式: | SMALL OUTLINE, SHRINK PITCH | 筛选级别: | TS 16949 |

| 座面最大高度: | 2 mm | 最大供电电压: | 5.5 V |

| 最小供电电压: | 2 V | 标称供电电压: | 5 V |

| 表面贴装: | YES | 技术: | CMOS |

| 温度等级: | INDUSTRIAL | 端子形式: | GULL WING |

| 端子节距: | 0.65 mm | 端子位置: | DUAL |

| 宽度: | 5.3 mm | uPs/uCs/外围集成电路类型: | PARALLEL IO PORT, GENERAL PURPOSE |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| MCP23016T-I/ML | MICROCHIP | 16 BIT I/O EXPANDER, -40C to +85C, 28-QFN, T/R |

获取价格 |

|

| MCP23016T-I/SS | MICROCHIP | 16 BIT I/O EXPANDER, -40C to +85C, 28-SSOP 208mil, T/R |

获取价格 |

|

| MCP23017 | MICROCHIP | 16-Bit I/O Expander with Serial Interface |

获取价格 |

|

| MCP23017-E/ML | MICROCHIP | 16-Bit I/O Expander with Serial Interface |

获取价格 |

|

| MCP23017-E/MLT | MICROCHIP | Parallel I/O Port, 16 I/O, CMOS, PQCC28 |

获取价格 |

|

| MCP23017-E/SO | MICROCHIP | 16-Bit I/O Expander with Serial Interface |

获取价格 |

|

MC34063开关稳压器:全面参数解析与设计指南

MC34063开关稳压器:全面参数解析与设计指南

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

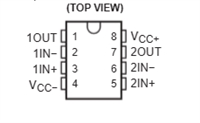

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析