| 生命周期: | Obsolete | 包装说明: | GREEN, METAL, TO-99, 8 PIN |

| Reach Compliance Code: | unknown | 风险等级: | 5.66 |

| Is Samacsys: | N | 放大器类型: | OPERATIONAL AMPLIFIER |

| 标称共模抑制比: | 80 dB | 最大输入失调电压: | 1000 µV |

| JESD-30 代码: | O-MBCY-W8 | JESD-609代码: | e4 |

| 功能数量: | 1 | 端子数量: | 8 |

| 最高工作温度: | 125 °C | 最低工作温度: | -55 °C |

| 封装主体材料: | METAL | 封装代码: | TO-99 |

| 封装形状: | ROUND | 封装形式: | CYLINDRICAL |

| 峰值回流温度(摄氏度): | NOT SPECIFIED | 认证状态: | Not Qualified |

| 标称压摆率: | 2.6 V/us | 供电电压上限: | 22 V |

| 标称供电电压 (Vsup): | 15 V | 表面贴装: | NO |

| 温度等级: | MILITARY | 端子面层: | GOLD |

| 端子形式: | WIRE | 端子位置: | BOTTOM |

| 处于峰值回流温度下的最长时间: | NOT SPECIFIED | Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| INA117KU/2K5 | TI | High Common-Mode Voltage DIFFERENCE AMPLIFIER |

获取价格 |

|

| INA117KU/2K5G4 | TI | High Common-Mode Voltage DIFFERENCE AMPLIFIER |

获取价格 |

|

| INA117KUG4 | TI | High Common-Mode Voltage DIFFERENCE AMPLIFIER |

获取价格 |

|

| INA117P | BB | High Common-Mode Voltage DIFFERENCE AMPLIFIER |

获取价格 |

|

| INA117P | TI | High Common-Mode Voltage DIFFERENCE AMPLIFIER |

获取价格 |

|

| INA117P-BI | TI | High Common-Mode Voltage DIFFERENCE AMPLIFIER |

获取价格 |

|

pcf8563芯片功能说明、参数分析、引脚说明

pcf8563芯片功能说明、参数分析、引脚说明

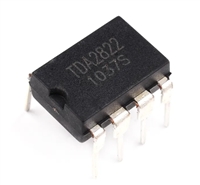

TDA2822资料手册:引脚说明、参数分析

TDA2822资料手册:引脚说明、参数分析

TJA1050资料数据分析、引脚说明、应用示例介绍

TJA1050资料数据分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍