DS3181/DS3182/DS3183/DS3184

TABLE OF CONTENTS

1

2

3

BLOCK DIAGRAMS

APPLICATIONS

FEATURE DETAILS

14

15

17

3.1 GLOBAL FEATURES .......................................................................................................................17

3.2 RECEIVE DS3/E3/STS-1 LIU FEATURES.......................................................................................17

3.3 RECEIVE DS3/E3 FRAMER FEATURES ...........................................................................................17

3.4 RECEIVE PLCP FRAMER FEATURES ..............................................................................................18

3.5 RECEIVE CELL PROCESSOR FEATURES .........................................................................................18

3.6 RECEIVE PACKET PROCESSOR FEATURES .....................................................................................18

3.7 RECEIVE FIFO FEATURES.............................................................................................................19

3.8 RECEIVE SYSTEM INTERFACE FEATURES .......................................................................................19

3.9 TRANSMIT SYSTEM INTERFACE FEATURES .....................................................................................19

3.10 TRANSMIT FIFO FEATURES...........................................................................................................19

3.11 TRANSMIT CELL PROCESSOR FEATURES .......................................................................................19

3.12 TRANSMIT PACKET PROCESSOR FEATURES ...................................................................................19

3.13 TRANSMIT PLCP FORMATTER FEATURES ......................................................................................20

3.14 TRANSMIT DS3/E3 FORMATTER FEATURES ...................................................................................20

3.15 TRANSMIT DS3/E3/STS-1 LIU FEATURES.....................................................................................20

3.16 JITTER ATTENUATOR FEATURES ....................................................................................................20

3.17 CLOCK RATE ADAPTER FEATURES.................................................................................................20

3.18 HDLC OVERHEAD CONTROLLER FEATURES ..................................................................................20

3.19 FEAC CONTROLLER FEATURES ....................................................................................................21

3.20 TRAIL TRACE BUFFER FEATURES...................................................................................................21

3.21 BIT ERROR RATE TESTER (BERT) FEATURES................................................................................21

3.22 LOOPBACK FEATURES...................................................................................................................21

3.23 MICROPROCESSOR INTERFACE FEATURES.....................................................................................21

3.24 SUBRATE FEATURES (FRACTIONAL DS3/E3)..................................................................................21

3.25 TEST FEATURES............................................................................................................................22

4

5

6

STANDARDS COMPLIANCE

ACRONYMS AND GLOSSARY

MAJOR OPERATIONAL MODES

23

25

26

6.1 DS3/E3 ATM/PACKET MODE ........................................................................................................26

6.2 DS3/E3 ATM/PACKET—OHM MODE............................................................................................27

6.3 DS3/E3 INTERNAL FRACTIONAL (SUBRATE) ATM/PACKET MODE...................................................28

6.4 DS3/E3 EXTERNAL FRACTIONAL (SUBRATE) ATM/PACKET MODE..................................................29

6.5 DS3/E3 FLEXIBLE EXTERNAL FRACTIONAL (SUBRATE) MODE CONFIGURATION MODE ....................30

6.6 DS3/E3 G.751 PLCP ATM MODE................................................................................................31

6.7 DS3/E3 G.751 PLCP ATM—OHM MODE....................................................................................32

6.8 CLEAR-CHANNEL ATM/PACKET MODE...........................................................................................34

6.9 CLEAR-CHANNEL ATM/PACKET—OHM MODE ..............................................................................35

6.10 CLEAR-CHANNEL OCTET ALIGNED ATM/PACKET—OHM MODE.....................................................36

7

8

MAJOR LINE INTERFACE OPERATING MODES

37

7.1 DS3HDB3/B3ZS/AMI LIU MODE .................................................................................................37

7.2 HDB3/B3ZS/AMI NON-LIU LINE INTERFACE MODE.......................................................................39

7.3 UNI LINE INTERFACE MODE ..........................................................................................................40

7.4 UNI LINE INTERFACE—OHM MODE ..............................................................................................41

PIN DESCRIPTIONS

42

3

74HC245八路双向总线收发器:资料手册参数分析

74HC245八路双向总线收发器:资料手册参数分析

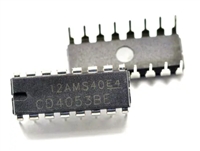

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

PCM1794音频DAC:全面参数解析与关键特性指南

PCM1794音频DAC:全面参数解析与关键特性指南