| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| CY54FCT273TLCC | TI |

获取价格 |

8-Bit Register |

|

| CY54FCT273TLM | CYPRESS |

获取价格 |

D Flip-Flop, FCT Series, 1-Func, Positive Edge Triggered, 8-Bit, True Output, CMOS, CQCC20 |

|

| CY54FCT273TQSOP | TI |

获取价格 |

8-Bit Register |

|

| CY54FCT273TSOIC | TI |

获取价格 |

8-Bit Register |

|

| CY54FCT2827ATDM | ETC |

获取价格 |

10-Bit Buffer/Driver |

|

| CY54FCT2827ATDMB | CYPRESS |

获取价格 |

Bus Driver, FCT Series, 1-Func, 10-Bit, True Output, CMOS, CDIP24, 0.300 INCH, CERDIP-24 |

|

| CY54FCT2827ATLM | ETC |

获取价格 |

10-Bit Buffer/Driver |

|

| CY54FCT2827ATLMB | CYPRESS |

获取价格 |

Bus Driver, FCT Series, 1-Func, 10-Bit, True Output, CMOS, CQCC28, CERAMIC, LCC-28 |

|

| CY54FCT2827BTDM | ETC |

获取价格 |

10-Bit Buffer/Driver |

|

| CY54FCT2827BTDMB | CYPRESS |

获取价格 |

Bus Driver, FCT Series, 1-Func, 10-Bit, True Output, CMOS, CDIP24, 0.300 INCH, CERDIP-24 |

|

芯片底部填充工艺:提升电子设备可靠性的关键步骤

芯片底部填充工艺:提升电子设备可靠性的关键步骤

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

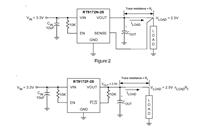

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明