| 生命周期: | Obsolete | 包装说明: | DIE, |

| Reach Compliance Code: | unknown | HTS代码: | 8542.39.00.01 |

| 风险等级: | 5.65 | 系列: | HCT |

| JESD-30 代码: | X-XUUC-N14 | 逻辑集成电路类型: | NAND GATE |

| 功能数量: | 3 | 输入次数: | 3 |

| 端子数量: | 14 | 最高工作温度: | 125 °C |

| 最低工作温度: | -55 °C | 封装主体材料: | UNSPECIFIED |

| 封装代码: | DIE | 封装形状: | UNSPECIFIED |

| 封装形式: | UNCASED CHIP | 传播延迟(tpd): | 36 ns |

| 认证状态: | Not Qualified | 最大供电电压 (Vsup): | 5.5 V |

| 最小供电电压 (Vsup): | 4.5 V | 标称供电电压 (Vsup): | 5 V |

| 表面贴装: | YES | 技术: | CMOS |

| 温度等级: | MILITARY | 端子形式: | NO LEAD |

| 端子位置: | UPPER | Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| CD54HCT10H/3A | RENESAS |

获取价格 |

HCT SERIES, TRIPLE 3-INPUT NAND GATE, UUC14 |

|

| CD54HCT10M | ETC |

获取价格 |

Logic IC |

|

| CD54HCT11 | TI |

获取价格 |

High Speed CMOS Logic Triple 3-Input AND Gate |

|

| CD54HCT112 | TI |

获取价格 |

Dual J-K Flip-Flop with Set and Reset Negative-Edge Trigger |

|

| CD54HCT112E | ETC |

获取价格 |

Logic IC |

|

| CD54HCT112EN | ETC |

获取价格 |

Logic IC |

|

| CD54HCT112F | RENESAS |

获取价格 |

HCT SERIES, DUAL NEGATIVE EDGE TRIGGERED J-K FLIP-FLOP, COMPLEMENTARY OUTPUT, CDIP16 |

|

| CD54HCT112F | ROCHESTER |

获取价格 |

HCT SERIES, DUAL NEGATIVE EDGE TRIGGERED J-K FLIP-FLOP, COMPLEMENTARY OUTPUT, CDIP16 |

|

| CD54HCT112F/3 | RENESAS |

获取价格 |

HCT SERIES, DUAL NEGATIVE EDGE TRIGGERED J-K FLIP-FLOP, COMPLEMENTARY OUTPUT, CDIP16 |

|

| CD54HCT112F/3A | RENESAS |

获取价格 |

暂无描述 |

|

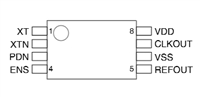

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

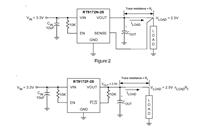

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明

一文带你了解SM8760CA资料:主要参数特征

一文带你了解SM8760CA资料:主要参数特征

解读MAX3238ECPW:一款多通道RS-232线驱动/接收器

解读MAX3238ECPW:一款多通道RS-232线驱动/接收器