在全球半导体产业加速变革的背景下,高性能计算(HPC)和人工智能(AI)的爆发式需求正推动芯片封装技术迎来新一轮革新。面对传统芯片制程逼近物理极限、研发成本飙升的挑战,先进封装技术成为突破“存储墙”和“面积墙”的关键。近期,国内半导体企业宣布斥资20亿元加码布局,以芯粒集成、面板级封装等创新技术抢占产业制高点。

算力需求爆发,先进封装成破局关键

随着AI算力需求呈指数级增长,芯片需处理的数据量激增,但传统SoC芯片在3nm以下制程遭遇量子隧穿效应和布线难题,性能提升陷入瓶颈。与此同时,3nm工艺研发成本高达数十亿美元,迫使行业寻求更经济的解决方案。先进封装技术通过模块化整合不同工艺、功能的芯片,成为高性能计算的破局利器。

以台积电3DFabric平台为例,其0.4μm线宽和50μm微凸点节距技术实现了高密度互连;苹果A系列处理器借助扇出封装集成190亿晶体管,英伟达H100 GPU则通过TSMC N4工艺实现80B晶体管集成,均彰显了先进封装在突破算力极限上的核心价值。

国产技术突围:12英寸晶圆级封装与面板级创新

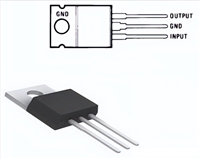

国内企业正快速跟进这一趋势。中科芯依托全产业链优势,率先突破12英寸晶圆级扇出封装技术,实现5μm线宽/线距和10:1 TSV深宽比,其2.5D硅桥方案支持1024bit/4.8mm高速互连,并通过30W高功耗可靠性验证。此外,面板级封装(PLP)技术因成本优势备受关注。扇出型面板级封装可替代硅中介层,降低成本的同时支持高I/O数量芯片集成,已成为智能手表、物联网设备的主流选择。

据预测,全球面板级封装市场规模将从2024年的1.6亿美元飙升至2030年的6.5亿美元,年复合增长率超25%。国内企业正加速布局玻璃基板和有机中介层技术,以应对AI和HPC对超大尺寸封装的需求。

20亿资金注入,产业链协同发力

为抢占技术高地,国内半导体企业近期宣布投入20亿元,重点推动晶圆级封装产线建设和面板级工艺研发。项目涵盖TSV通孔、高密度布线、低翘曲材料等核心技术,目标在2027年前实现5μm以下线宽量产能力,并建立自主知识产权体系。

业界专家指出,此次投资将加速国产封装技术从“跟跑”转向“并跑”,尤其在AI芯片、车规级芯片等高端领域,国产先进封装有望成为全球供应链的关键一环。随着摩尔定律放缓,以封装创新驱动芯片性能提升的“后摩尔时代”已至,中国半导体产业正迎来弯道超车的历史机遇。

未来,随着3D堆叠、异质集成等技术的成熟,先进封装将进一步推动芯片高性能、小型化与集成化,成为全球半导体竞争的新赛道。国内企业的战略布局,或将重塑产业格局。

浙公网安备 33010502006866号

浙公网安备 33010502006866号