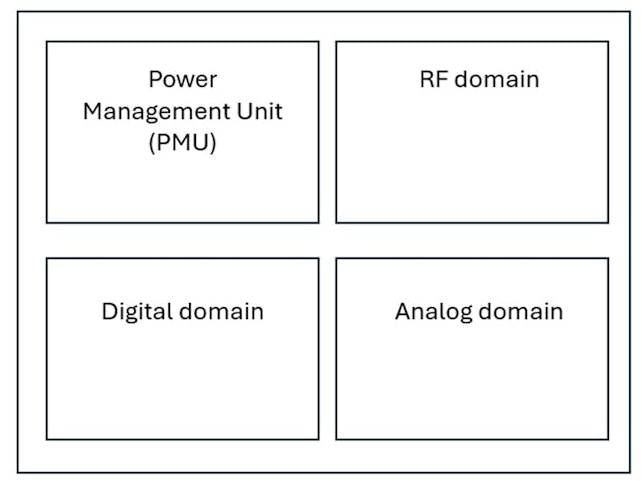

在当今的电子技术领域,无线片上系统(SoC)设计正发挥着越来越重要的作用。无线SoC设计的一大优势在于能够在同一芯片上实现所有电路域,这不仅有助于制造商降低成本,还能增强系统的完整性。然而,这种集成方式也带来了一个棘手的问题——不同电路域之间的串扰,尤其是射频(RF)耦合问题,这可能会严重降低系统的整体性能。

RF耦合通道分析

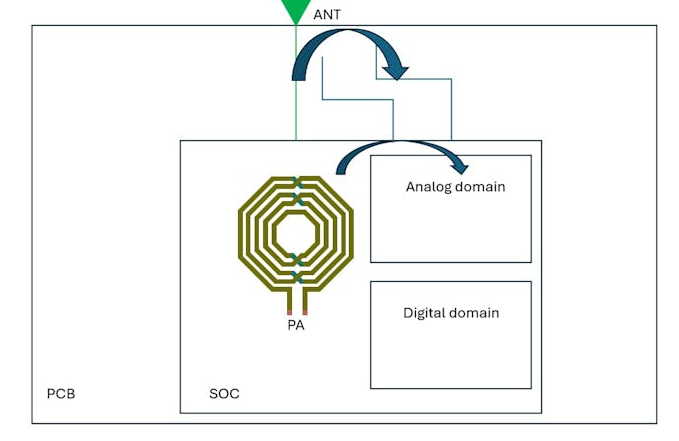

电磁干扰(EMI)是由辐射射频(RF)信号引发的。在系统设计中,虽然可以采用滤波和屏蔽等技术来应对辐射射频,但这些方法对于片上RF耦合却效果不佳。RF耦合是RF域和其他域之间串扰的典型例子。以无线发射器为例,它需要产生大约在10dBm范围内的输出功率,而功率放大器(PA)在产生这些功率的过程中,有时会包含片上电感或变压器。由于电感的电磁辐射,一小部分发射功率会耦合到SoC内的其他域。无论耦合分量是处于相同的发射频率还是谐波,都会对收发器的性能产生负面影响。当集成频率合成器的输出信号频谱变得杂散时,这种影响就会变得十分明显。此外,相同的耦合机制也可能在SoC外部的PCB级别发生,天线辐射的信号会影响附近其他域的关键PCB布线。

(图1.带注释的域通常位于无线SoC中)

(图2.箭头表示无线模块中可能的射频耦合机制)

减少RF耦合的方法

通常情况下,任何以任意频率(f₁)运行的区块都可能成为以另一个频率(f₂)运行的受害者区块的攻击者,反之亦然。不过,当一个频率是另一个频率的精确整数倍时,可能会出现特殊情况。攻击者影响受害者的链接主要包括供应网络、寄生电容耦合、寄生磁耦合和基板耦合。以下是针对不同耦合途径的具体解决方法:

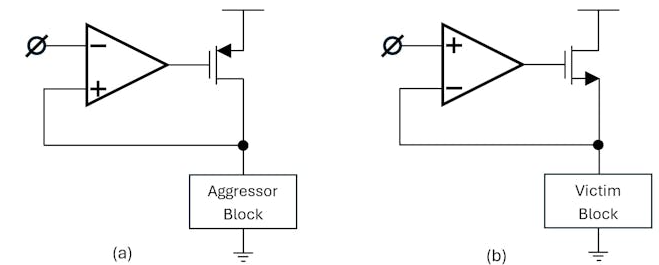

减少供应网络耦合

使用不同稳压器:对于对电源噪声不敏感的攻击模块,可以采用并联稳压器供电。因为并联稳压器的反向电源抑制比(PSRR)较小,能够有效保护电源免受干扰。而对于对电源噪声敏感且对电源污染影响可忽略不计的模块,则应由串联稳压器供电,串联稳压器的正向PSRR小,能保护敏感模块免受电源噪声干扰。

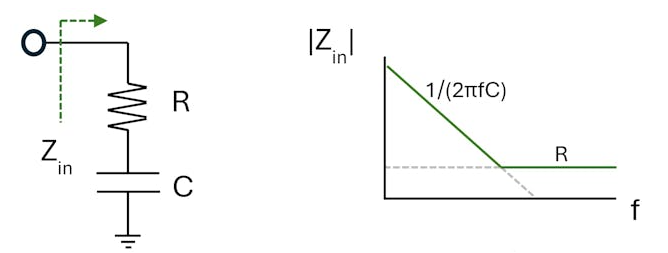

添加电源去耦电容:在每个模块附近添加充足的电源去耦电容是减少电源网络耦合的常见方法。但在操作时需要格外谨慎,要尽量降低去耦电容布线的寄生电阻,以提高其品质因数。当使用MOS器件实现去耦电容器时,应缩短单元去耦电容器的长度,减小其通道电阻。因为与寄生电阻串联的电容器在高频时,其阻抗会达到寄生电阻值饱和,从而影响去耦效果。

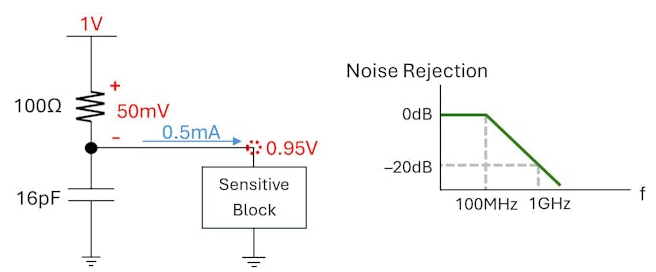

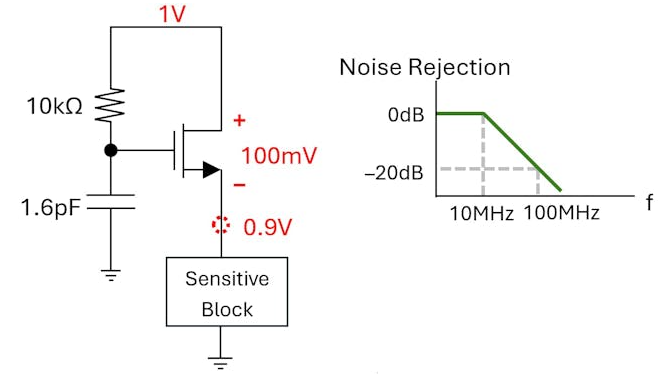

添加电源滤波器:虽然添加无源或有源电源滤波器可能会导致电源电压裕量损失,但在某些情况下是可行的。例如,对于一个具有1V电源且功耗为0.5mA的模块,插入100Ω电阻器仅会使电源裕量减少50mV。当添加16pF的滤波器电容时,可实现1GHz电源噪声衰减20dB。对于利用原生NMOS器件的面积高效有源滤波器,也能达到类似的效果,且能大大降低滤波器电容,实现紧凑设计。

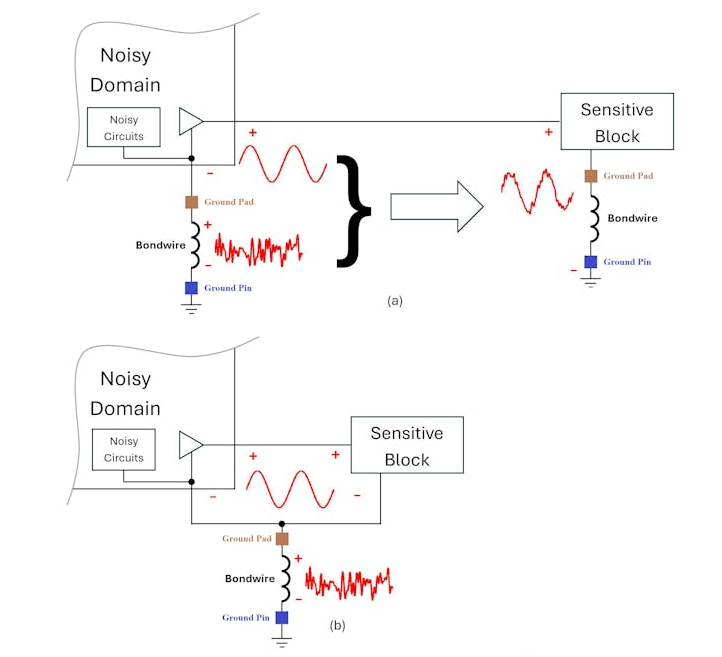

合理处理接地连接:将不同模块的接地连接分开并连接到不同的焊盘可能会导致严重问题,这种分离不仅无法隔离敏感块,反而会污染它们。因此,应采用共享接地焊盘的方式,以确保敏感模块输入信号的安全传输。

(图3.并联稳压器保护电源免受干扰器阻塞(a)。串联稳压器保护敏感模块免受电源噪声(b))

(图4.与电源去耦电容串联的寄生电阻器会降低其性能)

(图5.这是无源电源滤波器设计中电源裕量和噪声过滤之间合理权衡的一个例子)

(图6.有源电源滤波器的滤波器电容可以大大降低,从而实现紧凑的设计)

(图7.当通信域的接地焊盘分离时,敏感模块的输入信号可能会受到污染(a)。当共享接地焊盘时,可以安全地传输相同的信号(b))

减少寄生电容耦合:寄生电容耦合问题主要在布局级别解决。敏感和嘈杂的节点应使用其参考电源轨进行屏蔽,合理的接地平面设计也有助于减少寄生电容耦合。此外,由于电容与导体之间的距离成反比,增加走线之间的间距也能起到一定的作用。

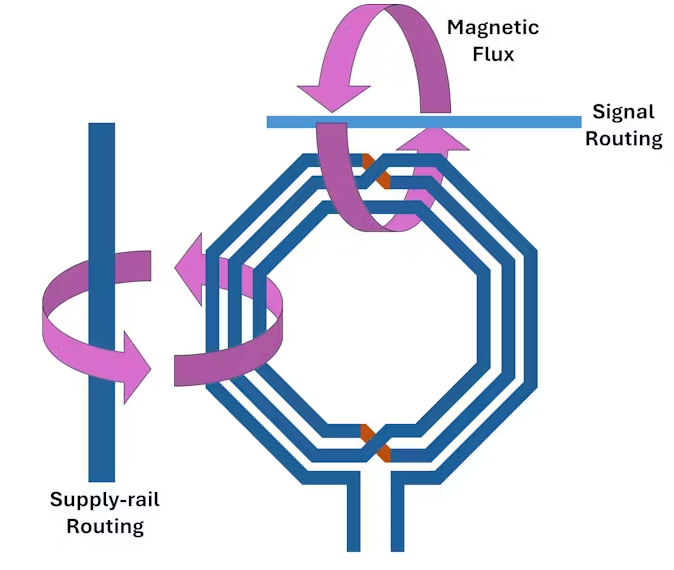

减少寄生磁耦合:当长路线方向相同时,它们之间容易发生磁耦合,尤其是在通往螺旋线圈一侧的长平行路线之间,这种耦合更为明显。特别是当线圈同时承载高频和大幅度的电流时,如功率放大器的情况,磁耦合问题会更加严重。为了减少这种磁耦合,敏感路线应尽量远离线圈和其他噪声路线。同时,当布线彼此正交时,磁耦合会大幅减小。

(图8.螺旋线圈和相邻长路线之间的磁耦合是一个严重的问题)

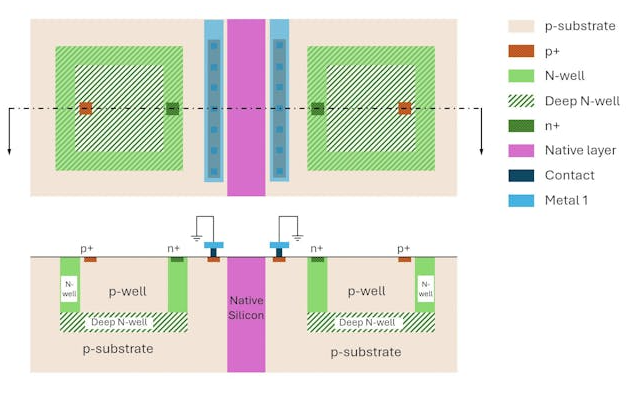

减少基板耦合:有时,噪声会通过衬底发生耦合。为了克服这个问题,可以使用深N孔层将不同的电路隔离到井中。同时,在隔离域之间添加高电阻率固有层,并使相邻的体连接为不同的接地焊盘提供低阻抗路径。

(图9.在使用深N孔和天然层的布局中可以实现结构域底物的分离)

其他减少噪声传输的准则

除了上述针对不同耦合途径的解决方法外,还可以遵循一些准则来进一步减少噪声从一个域到另一个域的传输。例如,应尽可能使用差分信号进行域间连接,这样可以最大限度地减少参考节点噪声的传递。此外,故意削弱一个域边界的信号驱动器,能够减少所有信号到其他域的电传输,这种方法在处理CMOS逻辑信号(如高速时钟和数字总线)时非常有效。

无线SoC系统中的RF耦合问题是一个不容忽视的挑战,它可能会对系统的整体性能产生严重影响。在进行SoC布局规划并识别攻击和受害模块时,必须给予足够的重视。通过实施上述耦合减少技术,能够有效提高系统的性能,满足设计要求。

490

490

浙公网安备 33010502006866号

浙公网安备 33010502006866号