| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| AGLN010V2-ZVQG100PP | MICROSEMI |

获取价格 |

IGLOO nano Low Power Flash FPGAs with Flash*Freeze Technology |

|

| AGLN010V2-ZVQG100Y | MICROSEMI |

获取价格 |

IGLOO nano Low Power Flash FPGAs with Flash*Freeze Technology |

|

| AGLN010V2-ZVQG100YES | MICROSEMI |

获取价格 |

IGLOO nano Low Power Flash FPGAs with Flash*Freeze Technology |

|

| AGLN010V2-ZVQG100YI | MICROSEMI |

获取价格 |

IGLOO nano Low Power Flash FPGAs with Flash*Freeze Technology |

|

| AGLN010V2-ZVQG100YPP | MICROSEMI |

获取价格 |

IGLOO nano Low Power Flash FPGAs with Flash*Freeze Technology |

|

| AGLN010V2-ZVQG81 | MICROSEMI |

获取价格 |

IGLOO nano Low Power Flash FPGAs with Flash*Freeze Technology |

|

| AGLN010V2-ZVQG81ES | MICROSEMI |

获取价格 |

IGLOO nano Low Power Flash FPGAs with Flash*Freeze Technology |

|

| AGLN010V2-ZVQG81I | MICROSEMI |

获取价格 |

IGLOO nano Low Power Flash FPGAs with Flash*Freeze Technology |

|

| AGLN010V2-ZVQG81PP | MICROSEMI |

获取价格 |

IGLOO nano Low Power Flash FPGAs with Flash*Freeze Technology |

|

| AGLN010V2-ZVQG81Y | MICROSEMI |

获取价格 |

IGLOO nano Low Power Flash FPGAs with Flash*Freeze Technology |

|

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

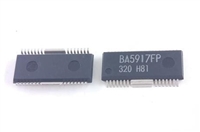

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐