Data Sheet

ADuM120N/ADuM121N

ELECTRICAL CHARACTERISTICS—3.3 V OPERATION

All typical specifications are at TA = 25°C, VDD1 = VDD2 = 3.3 V. Minimum/maximum specifications apply over the entire recommended

operation range: 3.0 V ≤ VDD1 ≤ 3.6 V, 3.0 V ≤ VDD2 ≤ 3.6 V, and −40°C ≤ TA ≤ +125°C, unless otherwise noted. Switching specifications

are tested with CL = 15 pF and CMOS signal levels, unless otherwise noted. Supply currents are specified with 50% duty cycle signals.

Table 3.

Parameter

Symbol

Min

Typ

Max

Unit

Test Conditions/Comments

SWITCHING SPECIFICATIONS

Pulse Width

Data Rate

Propagation Delay

Pulse Width Distortion

Change vs. Temperature

Propagation Delay Skew

PW

6.6

150

4.8

ns

Mbps

ns

ns

ps/°C

ns

Within PWD limit

Within PWD limit

50% input to 50% output

|tPLH − tPHL|

tPHL, tPLH

PWD

6.8

0.7

1.5

14

3

tPSK

7.0

Between any two units at the same

temperature, voltage, and load

Channel Matching

Codirectional

Opposing Direction

Jitter

tPSKCD

tPSKOD

0.7

0.7

290

45

3.0

3.0

ns

ns

ps p-p

ps rms

See the Jitter Measurement section

See the Jitter Measurement section

DC SPECIFICATIONS

Input Threshold Voltage

Logic High

VIH

VIL

0.7 × VDDx

V

V

Logic Low

0.3 × VDDx

Output Voltage

Logic High

2

VOH

VOL

II

VDDx − 0.1

VDDx − 0.4

VDDx

VDDx − 0.2

0.0

0.2

+0.01

V

V

V

V

IOx1 = −20 µA, VIx = VIxH

2

IOx1 = −2 mA, VIx = VIxH

3

Logic Low

0.1

0.4

+10

IOx1 = 20 µA, VIx = VIxL

3

IOx1 = 2 mA, VIx = VIxL

Input Current per Channel

Quiescent Supply Current

ADuM120N

−10

µA

0 V ≤ VIx ≤ VDDx

IDD1 (Q)

IDD2 (Q)

IDD1 (Q)

IDD2 (Q)

IDD1 (Q)

IDD2 (Q)

IDD1 (Q)

IDD2 (Q)

0.8

1.2

6.3

1.3

1.0

1.0

3.9

4.8

1.3

1.8

9.7

1.8

1.6

1.5

5.8

6.4

mA

mA

mA

mA

mA

mA

mA

mA

VI4 = 0 (N0), 1 (N1)5

VI4 = 0 (N0), 1 (N1)5

VI4 = 1 (N0), 0 (N1)5

VI4 = 1 (N0), 0 (N1)5

VI4 = 0 (N0), 1 (N1)5

VI4 = 01 (N0), 1 (N1)5

VI4 = 1 (N0), 0 (N1)5

VI4 = 1 (N0), 0 (N1)5

ADuM121N

Dynamic Supply Current

Dynamic Input

Dynamic Output

Undervoltage Lockout

Positive VDDx Threshold

Negative VDDx Threshold

VDDx Hysteresis

IDDI (D)

0.01

0.01

mA/Mbps

mA/Mbps

Inputs switching, 50% duty cycle

Inputs switching, 50% duty cycle

IDDO (D)

UVLO

VDDxUV+

VDDxUV−

VDDxUVH

1.6

1.5

0.1

V

V

V

Rev. A | Page 5 of 19

pcf8563芯片功能说明、参数分析、引脚说明

pcf8563芯片功能说明、参数分析、引脚说明

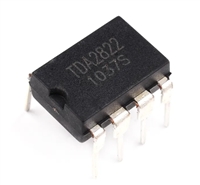

TDA2822资料手册:引脚说明、参数分析

TDA2822资料手册:引脚说明、参数分析

TJA1050资料数据分析、引脚说明、应用示例介绍

TJA1050资料数据分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍