®

®

ADCDS-1405

Non-Inverting Mode

Inverting Mode

The non-inverting mode of the ADCDS-1405 allows the

designer to either attenuate or add non-inverting gain to the

video input signal. This configuration also allows bypassing

the ADCDS-1405's internal coupling capacitor, allowing the

user to provide an external capacitor of appropriate value.

The inverting mode of operation can be used in applications

where the analog input to the ADCDS-1405 has a video input

signal whose amplitude is more positive than its associated

reference level. The ADCDS-1405s correlated double

sampler (i.e. input amplifier's VOUT) requires that the video

signal's amplitude be more negative than its reference

Figure 2c. describes the typical configuration for applications

using video input signals with amplitudes greater than

0.350Vp-p and less than 2.8Vp-p (with common mode limit of

±2.5V DC). Using a single external series resistor (see

Figure 4.), the coarse gain of the ADCDS-1405 can be set

with additional fine gain adjustments being made using the

Fine Gain Adjust function (pin 1 see Figure 5). The coarse

gain of the circuit can be determined from the following

equation:

level at all times (see timing diagram for details). Using the

ADCDS-1405 in the inverting mode allows the designer to

perform an additional signal inversion to correct for any

analog "front end" pre-processing that may have occurred

prior to the ADCDS-1405.

Figure 2e. describes the typical configuration for applications

using a video input signal with a maximum amplitude of

0.350Vp-p. Additional fine gain adjustments can be made

using the Fine Gain Adjust function (pin 1). The coarse gain

of this circuit can be determined from the following equation:

VOUT = 2.8Vp-p = –VIN*(523/75), with all internal resistors

having a 1% tolerance.

VOUT = 2.8Vp-p = VIN*(1+(523/(75+Rext))), with all internal

resistors having a 1% tolerance.

Figure 2d. describes the typical configuration for applications

using a video input signal whose amplitude is greater than

2.8Vp-p. Using a single external series resistor (Rext 1) in

conjunction with the internal 5K (1%) resistor to ground, an

attenuation of the input signal can be achieved. Additional fine

gain adjustments being made using the Fine Gain Adjust

function (pin 1). The coarse gain of this circuit can be

determined from the following equation:

Figure 2f. describes the typical configuration used in

applications needing to invert video input signals whose

amplitude is greater than 0.350Vp-p. Using a single external

series resistor (see Figure 4.), the initial gain of the ADCDS-

1405 can be set, with additional fine gain adjustments being

made using the Fine Gain Adjust function (pin 1). The coarse

gain of this circuit can be determined from the following

equation:

VOUT = 2.8Vp-p = [VIN*(5000/(Rext1+5000))]*

[1+(523/(75+Rext2))], with all internal resistors having

a 1% tolerance.

VOUT = 2.8Vp-p = –VIN*(523/75+Rext), with all internal

resistors having a 1% tolerance.

Rext2

75

9

523

9

4

A

D

C

D

S

-

1

4

0

5

0.01µF

3

5

VOUT = 2.8Vp-p

NO CONNECT

Rext1

E

x

t

e

r

n

a

l

+

5

V

VIN

S

e

r

i

e

s

5k9

O

f

f

s

e

t

R

e

s

i

s

t

o

r

A

d

j

u

s

t

2

0

K

9

2

Figure 2d.

5

V

75

9

523

9

4

–VIN

Figure 3. Offset Adjustment Circuit

0.01µf

3

5

VOUT = 2.8Vp-p

NO CONNECT

5k9

C

o

a

r

s

e

G

a

i

n

A

d

j

u

s

t

m

e

n

t

P

l

o

t

E

x

t

e

r

n

a

l

G

a

i

n

R

e

s

i

s

t

o

r

v

s

.

F

u

l

l

S

c

a

l

e

V

i

d

e

o

I

n

p

u

t

1

0

0

0

0

Figure 2e.

D

&

M

i

r

e

c

t

M

o

d

e

N

o

n

-

I

n

v

e

r

t

i

n

g

1

0

0

0

o

d

e

Rext

75

9

523

9

4

–VIN

I

n

v

e

r

t

i

n

g

M

o

d

e

0.01µf

3

5

1

0

0

VOUT = 2.8Vp-p

NO CONNECT

5k

9

1

0

0

.

2

5

0

.

5

0

.

7

5

1

1

.

2

5

1

.

5

1

.

7

5

2

2

.

2

5

2

.

5

2

.

7

5

3

F

u

l

l

S

c

a

l

e

V

i

d

e

o

S

i

g

n

a

l

(

V

o

l

t

s

)

Figure 4. Coarse Gain Adjustment Plot

Figure 2f.

4

pcf8563芯片功能说明、参数分析、引脚说明

pcf8563芯片功能说明、参数分析、引脚说明

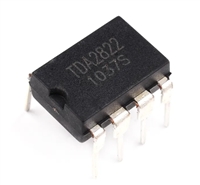

TDA2822资料手册:引脚说明、参数分析

TDA2822资料手册:引脚说明、参数分析

TJA1050资料数据分析、引脚说明、应用示例介绍

TJA1050资料数据分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍

DS3231时钟芯片:参数分析、引脚说明、应用示例介绍