Quad Analog-to-Digital Converter (ADC)

Data Sheet

ADAU1978

FEATURES

GENERAL DESCRIPTION

Four 2 V rms differential inputs

On-chip phase-locked loop (PLL) for master clock

Low electromagnetic interference (EMI) design

The ADAU1978 incorporates four high performance, analog-to-

digital converters (ADCs) with 2 V rms capable ac-coupled inputs.

The ADCs use a multibit sigma-delta (Σ-Δ) architecture with

continuous time front end for low EMI. An I2C/serial peripheral

interface (SPI) control port is included that allows a microcontroller

to adjust volume and many other parameters. The ADAU1978

uses only a single 3.3 V supply. The part internally generates the

required digital DVDD supply. The low power architecture

reduces the power consumption. The ADAU1978 is available in

a 40-lead LFCSP package. The on-chip PLL can derive the master

clock from an external clock input or frame clock (sample rate

clock). When fed with the frame clock, it eliminates the need

for a separate high frequency master clock in the system.

106 dB analog-to-digital converter (ADC) dynamic range

Total harmonic distortion + noise (THD + N): −95 dB

Selectable digital high-pass filter

24-bit stereo ADC with 8 kHz to 192 kHz sample rates

Digital volume control with autoramp function

I2C/SPI controllable for flexibility

Software-controllable clickless mute

Software power-down

Right justified, left justified, I2S, and TDM modes

Master and slave operation modes

40-lead LFCSP package

Qualified for automotive applications

Note that throughout this data sheet, multifunction pins, such

as SCL/CCLK, are referred to either by the entire pin name or

by a single function of the pin, for example, CCLK, when only

that function is relevant.

APPLICATIONS

Automotive audio systems

Active noise cancellation systems

FUNCTIONAL BLOCK DIAGRAM

3.3V TO 1.8V

REGULATOR

DVDD

ADAU1978

AIN1P

AIN1N

AIN2P

AIN2N

AIN3P

AIN3N

AIN4P

AIN4N

IOVDD

ADC

ADC

LRCLK

BCLK

ADC

ADC

SDATAOUT1

SDATAOUT2

AGND1

AVDD2

AGND3

SCL/CCLK

SDA/COUT

2

ADDR1/CIN

ADDR0/CLATCH

I C/SPI

BG

REF

CONTROL

PLL

PD/RST

AGND2

AGND2

Figure 1.

Rev. 0

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rightsof third parties that may result fromits use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks andregisteredtrademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

©2013 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

74HC245八路双向总线收发器:资料手册参数分析

74HC245八路双向总线收发器:资料手册参数分析

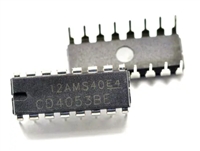

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4053模拟多路复用器/解复用器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

CD4011双4位二进制计数器:资料手册参数分析

PCM1794音频DAC:全面参数解析与关键特性指南

PCM1794音频DAC:全面参数解析与关键特性指南