932SQL456 DATASHEET

64VFQFPN Pin Descriptions

PIN #

PIN NAME

GNDPCI

TYPE

DESCRIPTION

1

2

3

4

5

6

7

8

9

PWR Ground pin for PCI outputs and logic.

PWR 3.3V power for the PCI outputs and logic

OUT 3.3V PCI clock output

OUT 3.3V PCI clock output

OUT 3.3V PCI clock output

OUT 3.3V PCI clock output

OUT 3.3V PCI clock output

PWR Ground pin for PCI outputs and logic.

PWR 3.3V power for the PCI outputs and logic

VDDPCI

PCI4_2x

PCI3_2x

PCI2_2x

PCI1_2x

PCI0_2x

GNDPCI

VDDPCI

10 VDD48

11 48M_2x

12 GND48

13 GND96

PWR 3.3V power for the 48MHz output and logic

OUT 3.3V 48MHz output

PWR Ground pin for 48MHz output and logic.

PWR Ground pin for DOT96 output and logic.

True clock of low-power push-pull differential 96MHz output. Internally terminated to drive 85ohm

transmission lines with no external components.

14 DOT96_Z85T

OUT

Complementary clock of low-power push-pull differential 96MHz output. Internally terminated to

drive 85ohm transmission lines with no external components.

PWR 3.3V power for the 48/96MHz PLL and the 96MHz output and logic

15 DOT96_Z85C

16 AVDD96

OUT

TEST_MODE is a real time input to select between Hi-Z and REF/N divider mode while in test

mode. Refer to Test Clarification Table.

17 TEST_MODE

IN

CKPWRGD# is an active low input used to sample latched inputs and allow the device to Power

IN Up. PD is an asynchronous active high input pin used to put the device into a low power state.

The internal clocks and PLLs are stopped.

18 CKPWRGD#/PD

19 VDDSRC

PWR 3.3V power for the SRC outputs and logic

True clock of low-power push-pull differential SRC output. Internally terminated to drive 85ohm

transmission lines with no external components.

20 SRC0_Z85T

OUT

Complementary clock of low-power push-pull differential SRC output. Internally terminated to

drive 85ohm transmission lines with no external components.

PWR Ground pin for SRC outputs and logic.

21 SRC0_Z85C

22 GNDSRC

OUT

Complementary clock of low-power push-pull differential SRC output. Internally terminated to

drive 85ohm transmission lines with no external components.

23 SRC1_Z85C

OUT

True clock of low-power push-pull differential SRC output. Internally terminated to drive 85ohm

transmission lines with no external components.

Complementary clock of low-power push-pull differential SRC output. Internally terminated to

drive 85ohm transmission lines with no external components.

True clock of low-power push-pull differential SRC output. Internally terminated to drive 85ohm

transmission lines with no external components.

24 SRC1_Z85T

25 SRC2_Z85C

26 SRC2_Z85T

OUT

OUT

OUT

27 VDDSRC

28 AVDD_SRC

29 GNDSRC

30 NC

PWR 3.3V power for the SRC outputs and logic

PWR 3.3V power for the SRC PLL analog circuits

PWR Ground pin for SRC outputs and logic.

N/A No Connection.

Complementary clock of low-power push-pull differential non-spreading SRC output. Internally

terminated to drive 85ohm transmission lines with no external components.

True clock of low-power push-pull differential non-spreading SRC output. Internally terminated to

drive 85ohm transmission lines with no external components.

Complementary clock of low-power push-pull differential non-spreading SRC output. Internally

terminated to drive 85ohm transmission lines with no external components.

True clock of low-power push-pull differential non-spreading SRC output. Internally terminated to

drive 85ohm transmission lines with no external components.

31 NS_SRC0_Z85C

32 NS_SRC0_Z85T

33 NS_SRC1_Z85C

34 NS_SRC1_Z85T

OUT

OUT

OUT

OUT

35 VDDNS

36 GNDNS

PWR 3.3V power for the Non-Spreading differential outputs outputs and logic

PWR Ground pin for non-spreading differential outputs and logic.

Complementary clock of low-power push-pull differential non-spreading SAS output. Internally

terminated to drive 85ohm transmission lines with no external components.

True clock of low-power push-pull differential non-spreading SAS output. Internally terminated to

drive 85ohm transmission lines with no external components.

37 NS_SAS0_Z85C

38 NS_SAS0_Z85T

OUT

OUT

LOW-POWER CK420BQ DERIVATIVE FOR PCIE SEPARATE CLOCK ARCHITECTURES

4

REVISION B 09/29/15

IRF3205功率MOSFET:资料手册参数分析

IRF3205功率MOSFET:资料手册参数分析

MC34063开关稳压器:全面参数解析与设计指南

MC34063开关稳压器:全面参数解析与设计指南

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

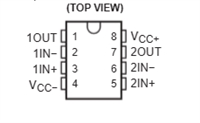

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析