| 是否Rohs认证: | 不符合 | 生命周期: | Obsolete |

| Reach Compliance Code: | not_compliant | 风险等级: | 5.92 |

| JESD-30 代码: | S-PQFP-G48 | JESD-609代码: | e0 |

| 湿度敏感等级: | 3 | 端子数量: | 48 |

| 最高工作温度: | 70 °C | 最低工作温度: | |

| 封装主体材料: | PLASTIC/EPOXY | 封装代码: | QFP |

| 封装等效代码: | QFP48,.35SQ,20 | 封装形状: | SQUARE |

| 封装形式: | FLATPACK | 电源: | 3.3 V |

| Prop。Delay @ Nom-Sup: | 2 ns | 认证状态: | Not Qualified |

| 子类别: | Clock Drivers | 标称供电电压 (Vsup): | 3.3 V |

| 表面贴装: | YES | 温度等级: | COMMERCIAL |

| 端子面层: | Tin/Lead (Sn85Pb15) | 端子形式: | GULL WING |

| 端子节距: | 0.5 mm | 端子位置: | QUAD |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| 8530DYI-01 | IDT | Clock Driver, 8530 Series, 16 True Output(s), 0 Inverted Output(s), PQFP48, 7 X 7 MM, 1 MM |

获取价格 |

|

| 8530DYI-01LF | IDT | Low Skew, 1-to-16 Differential-to-3.3V LVPECL Fanout Buffer |

获取价格 |

|

| 8530DYI-01LFT | IDT | Low Skew, 1-to-16 Differential-to-3.3V LVPECL Fanout Buffer |

获取价格 |

|

| 8530DYI-01T | IDT | Clock Driver, 8530 Series, 16 True Output(s), 0 Inverted Output(s), PQFP48, 7 X 7 MM, 1 MM |

获取价格 |

|

| 8530DYLF | IDT | Low Skew, 1-to16, Differential-to-2.5V LVPECL Fanout Buffer |

获取价格 |

|

| 8530DYLFT | IDT | Low Skew, 1-to16, Differential-to-2.5V LVPECL Fanout Buffer |

获取价格 |

|

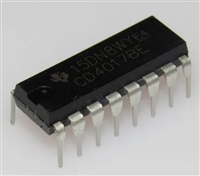

CD4017数据手册解析:参数分析、引脚说明、功能说明

CD4017数据手册解析:参数分析、引脚说明、功能说明

pcf8563芯片功能说明、参数分析、引脚说明

pcf8563芯片功能说明、参数分析、引脚说明

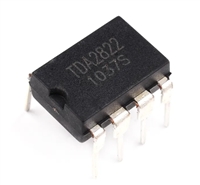

TDA2822资料手册:引脚说明、参数分析

TDA2822资料手册:引脚说明、参数分析

TJA1050资料数据分析、引脚说明、应用示例介绍

TJA1050资料数据分析、引脚说明、应用示例介绍