| 生命周期: | Active | 零件包装代码: | QFP |

| 包装说明: | FQFP, | 针数: | 208 |

| Reach Compliance Code: | compliant | ECCN代码: | 3A001.A.3 |

| HTS代码: | 8542.31.00.01 | 风险等级: | 5.77 |

| 地址总线宽度: | 32 | 总线兼容性: | PENTIUM PRO |

| 最大时钟频率: | 66 MHz | 最大数据传输速率: | 100 MBps |

| 外部数据总线宽度: | 32 | JESD-30 代码: | S-PQFP-G208 |

| 长度: | 28 mm | 端子数量: | 208 |

| 封装主体材料: | PLASTIC/EPOXY | 封装代码: | FQFP |

| 封装形状: | SQUARE | 封装形式: | FLATPACK, FINE PITCH |

| 认证状态: | Not Qualified | 座面最大高度: | 4.25 mm |

| 标称供电电压: | 3.3 V | 表面贴装: | YES |

| 技术: | CMOS | 端子形式: | GULL WING |

| 端子节距: | 0.5 mm | 端子位置: | QUAD |

| 宽度: | 28 mm | uPs/uCs/外围集成电路类型: | BUS CONTROLLER, PCI |

| Base Number Matches: | 1 |

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| 82-4425-1003 | AMPHENOL |

获取价格 |

RF N Connector, Male, Cable Mount, Crimp Terminal, Plug |

|

| 82-4426-1001 | AMPHENOL |

获取价格 |

RF N Connector, Male, Cable Mount, Crimp Terminal, Plug |

|

| 82-4426-11RFX | AMPHENOL |

获取价格 |

RF N Connector, 1 Contact(s), Male, Cable Mount, Crimp Terminal, Locking, Plug |

|

| 82442877U1000 | ETC |

获取价格 |

22 AWG stranded (7x30) tinned copper conductors, plenum, FEP insulation |

|

| 82442FX | INTEL |

获取价格 |

Microprocessor Circuit, CMOS, PQFP208, PLASTIC, QFP-208 |

|

| 82443BX | INTEL |

获取价格 |

Host Bridge/Controller |

|

| 82443EX | ETC |

获取价格 |

Controller Miscellaneous - Datasheet Reference |

|

| 82443GX | INTEL |

获取价格 |

Intel 440GX AGPset: 82443GX Host Bridge/Controller |

|

| 82443LX | INTEL |

获取价格 |

INTEL 440LX AGPSET: 82443LX PCI A.G.P. CONTROLLER (PAC) |

|

| 82443MX | INTEL |

获取价格 |

PCIset |

|

REF03GPZ资料解读:主要特征、技术参数、应用场景

REF03GPZ资料解读:主要特征、技术参数、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

一文带你了解DS28E40主要特征、安全特性、应用场景

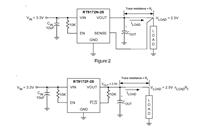

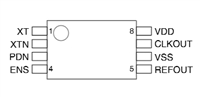

RT9172资料手册解读:关节特性、引脚信息、参数说明

RT9172资料手册解读:关节特性、引脚信息、参数说明

一文带你了解SM8760CA资料:主要参数特征

一文带你了解SM8760CA资料:主要参数特征