| 型号 | 品牌 | 描述 | 获取价格 | 数据表 |

| 70V659S12DRI8 | IDT | Dual-Port SRAM, 128KX36, 12ns, CMOS, PQFP208, 28 X 28 MM, 3.50 MM HEIGHT, PLASTIC, QFP-208 |

获取价格 |

|

| 70V659S15BC8 | IDT | CABGA-256, Reel |

获取价格 |

|

| 70V659S15BCG | IDT | HIGH-SPEED 3.3V 128/64/32K x 36 ASYNCHRONOUS DUAL-PORT STATIC RAM |

获取价格 |

|

| 70V659S15BCG8 | IDT | HIGH-SPEED 3.3V 128/64/32K x 36 ASYNCHRONOUS DUAL-PORT STATIC RAM |

获取价格 |

|

| 70V659S15BCGI | IDT | HIGH-SPEED 3.3V 128/64/32K x 36 ASYNCHRONOUS DUAL-PORT STATIC RAM |

获取价格 |

|

| 70V659S15BCGI8 | IDT | HIGH-SPEED 3.3V 128/64/32K x 36 ASYNCHRONOUS DUAL-PORT STATIC RAM |

获取价格 |

|

CC2530无线微控制器:资料手册参数分析

CC2530无线微控制器:资料手册参数分析

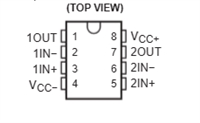

NE5532双低噪声运算放大器:资料手册参数分析

NE5532双低噪声运算放大器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析

74LS138 3-to-8线解码器/多路复用器:资料手册参数分析

TDA2030音频功率放大器:资料手册参数分析

TDA2030音频功率放大器:资料手册参数分析