| 生命周期: | Active | 零件包装代码: | DIP |

| 包装说明: | DIP, DIP24,.3 | 针数: | 24 |

| Reach Compliance Code: | not_compliant | ECCN代码: | EAR99 |

| HTS代码: | 8542.39.00.01 | 风险等级: | 5.14 |

| 边界扫描: | NO | 最大时钟频率: | 12.5 MHz |

| 外部数据总线宽度: | 8 | JESD-30 代码: | R-GDIP-T24 |

| 长度: | 32.005 mm | 低功率模式: | YES |

| 端子数量: | 24 | 最高工作温度: | 125 °C |

| 最低工作温度: | -55 °C | 输出数据总线宽度: | 8 |

| 封装主体材料: | CERAMIC, GLASS-SEALED | 封装代码: | DIP |

| 封装等效代码: | DIP24,.3 | 封装形状: | RECTANGULAR |

| 封装形式: | IN-LINE | 峰值回流温度(摄氏度): | NOT SPECIFIED |

| 电源: | 5 V | 认证状态: | Qualified |

| 筛选级别: | MIL-PRF-38535 | 座面最大高度: | 5.08 mm |

| 子类别: | DSP Peripherals | 最大供电电压: | 5.5 V |

| 最小供电电压: | 4.5 V | 标称供电电压: | 5 V |

| 表面贴装: | NO | 技术: | CMOS |

| 温度等级: | MILITARY | 端子形式: | THROUGH-HOLE |

| 端子节距: | 2.54 mm | 端子位置: | DUAL |

| 处于峰值回流温度下的最长时间: | NOT SPECIFIED | 宽度: | 7.62 mm |

| uPs/uCs/外围集成电路类型: | DSP PERIPHERAL, PIPELINE REGISTER | Base Number Matches: | 1 |

| 型号 | 品牌 | 替代类型 | 描述 | 数据表 |

| CY29FCT520ATPCE4 | TI |

类似代替  |

Multi-Level Pipeline Register |

|

| CY29FCT520BTSOCTE4 | TI |

类似代替  |

Multi-Level Pipeline Register |

|

| CY29FCT520ATPC | TI |

功能相似  |

Multi-Level Pipeline Register |

|

| 型号 | 品牌 | 获取价格 | 描述 | 数据表 |

| 5962-9220506M3A | ETC |

获取价格 |

Pipeline Register |

|

| 5962-9220506MKA | ETC |

获取价格 |

Pipeline Register |

|

| 5962-9220506MKX | WEDC |

获取价格 |

IC 8-BIT, DSP-PIPELINE REGISTER, CDFP24, CERPACK-24, DSP Peripheral |

|

| 5962-9220506MLA | ETC |

获取价格 |

Pipeline Register |

|

| 5962-9220506MLX | WEDC |

获取价格 |

IC 8-BIT, DSP-PIPELINE REGISTER, CDIP24, CERDIP-24, DSP Peripheral |

|

| 5962-9220601M2A | IDT |

获取价格 |

LCC-20, Tube |

|

| 5962-9220601M2X | ETC |

获取价格 |

8-Input Digital Multiplexer |

|

| 5962-9220601MEA | IDT |

获取价格 |

CDIP-16, Tube |

|

| 5962-9220601MEX | IDT |

获取价格 |

Multiplexer, FCT Series, 1-Func, 8 Line Input, 1 Line Output, Complementary Output, CMOS, |

|

| 5962-9220601MFA | WEDC |

获取价格 |

Multiplexer, FCT Series, 1-Func, 8 Line Input, 1 Line Output, Complementary Output, CMOS |

|

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

LTM4644/LTM4644-1:创新的四输出同步降压微模块调节器

2N3500:一款多用途NPN硅晶体管的全面解析

2N3500:一款多用途NPN硅晶体管的全面解析

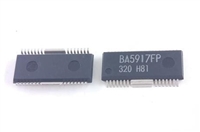

最详细资料解析:BA5917AFP参数说明、引脚说明

最详细资料解析:BA5917AFP参数说明、引脚说明

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐

MAX232IDR数据手册:产品特性、电气参数、替代型号推荐